STATus Subsystem Introduction

STATus Subsystem Introduction

The instrument uses a SCPI status system, which records various instrument conditions and states in several register

groups.

In this subsystem, an event is something that occurred, even though it may not still be occurring. A condition is some-

thing that is currently present. A condition will appear in the event register, but the event register is read destructive,

meaning they are cleared (set to 0) when read.

The STATus commandsmanipulate bits in two of the enable registers. You can:

l Enable bits in the Questionable Data enable register (STATus:QUEStionable:ENABle).

l Enable bits in the Operation enable register (STATus:OPERation:ENABle). Query: STATus:OPERation:ENABle?

l Clear all bits in the Questionable Data enable register and the Standard Operation enable register (STAT-

us:PRESet).

The STATus queries allow you to access information about the status bits in the Questionable Data registers,

including:

l The binary-weighted sum of all bits enabled in the Questionable Data condition register ( STAT-

us:QUEStionable:CONDition?)

l The binary-weighted sum of all bits enabled in the Questionable Data event register (STAT-

us:QUEStionable[:EVENt]?)

l The binary-weighted sum of all bits enabled in the Questionable Data enable register (STAT-

us:QUEStionable:ENABle?).

The STATus queries also allow you to access information about the status bits in the Operation registers, including:

l The binary-weighted sum of all bits enabled in the Operation condition register (STATus:OPERation:CONDition?).

l The binary-weighted sum of all bits enabled in the Operation event register (STATus:OPERation:EVENt?).

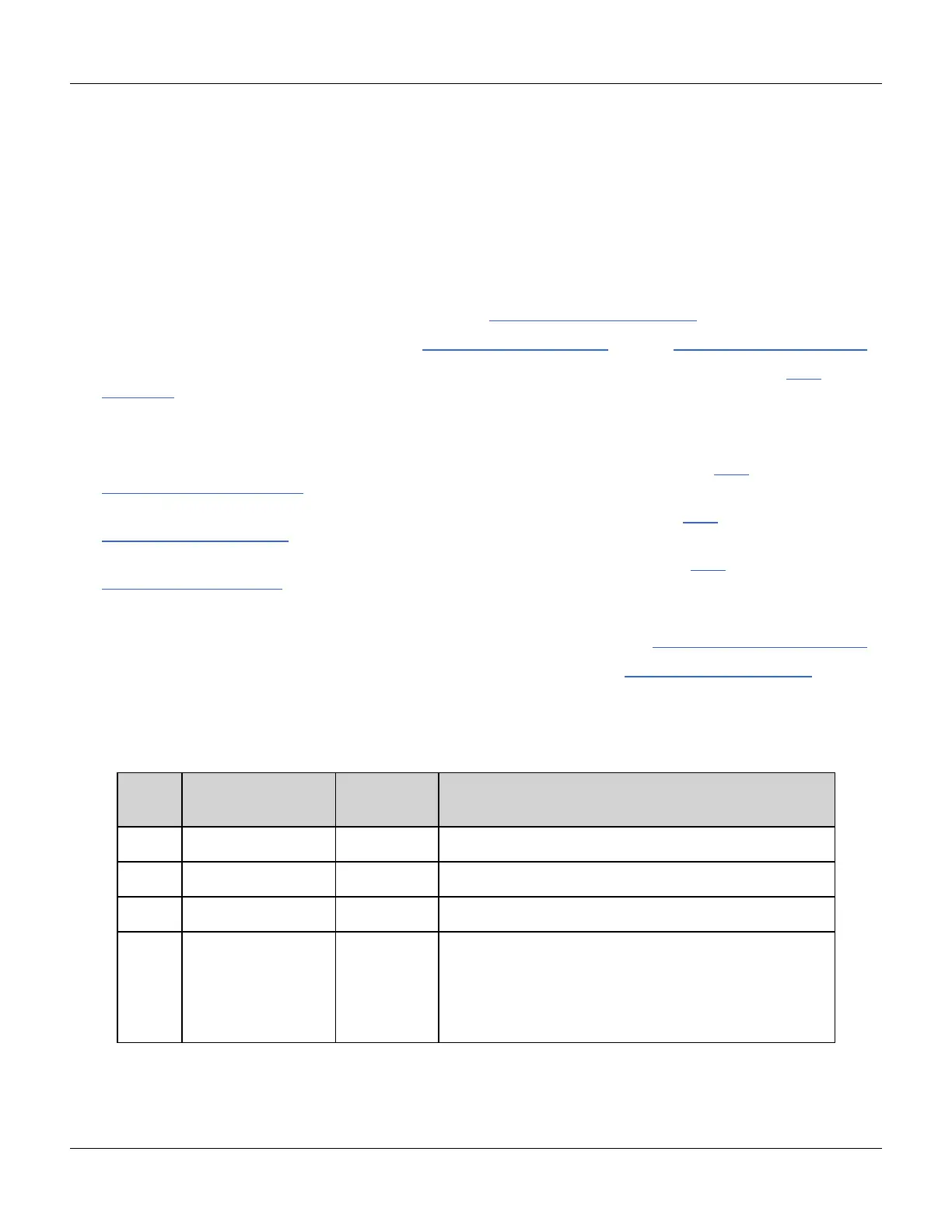

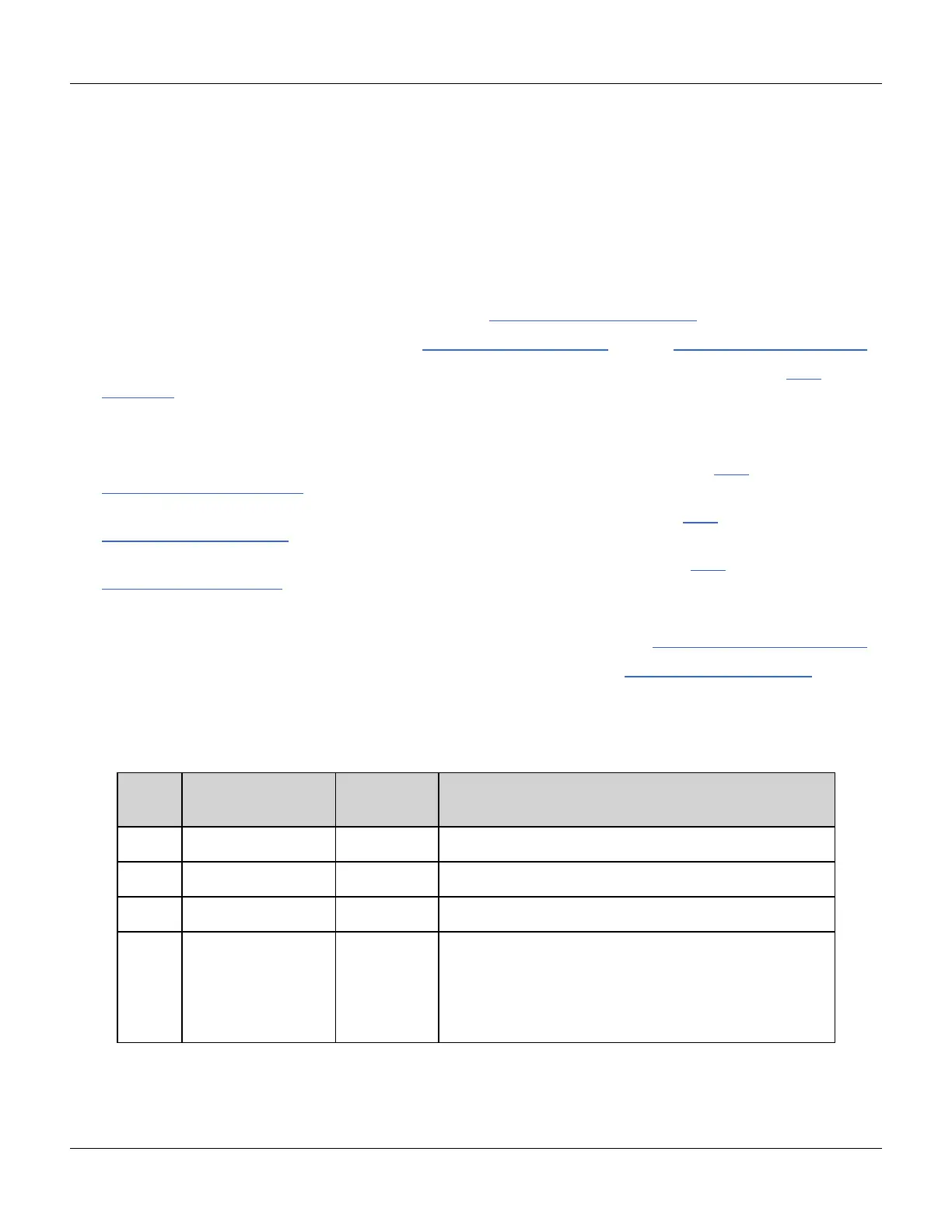

Standard Operation Register Group

The following table describes the Standard Operation Register group.

Bit Bit Name Decimal

Value

Definition

0 Calibrating 1 The instrument is performing a calibration.

1 Self-test 2 A self-test is running.

2 (Reserved) 4 (Reserved for future use)

3 Channel 1 Initiated 8 Channel is initiated and outputting the desired wave-

form. In INIT[1|2]:CONT OFF, this bit is set after receiv-

ing an INIT and not cleared until channel goes to IDLE (

trigger count satisfied and not busy.) This bit is 0 if the

channel is in INIT[1|2]:CONT ON mode.

Agilent 33500 Series Operating and Service Guide 285

Loading...

Loading...