ADV7511W HARDWARE USER’S GUIDE

Rev.A

Page 12

of 45

Rev A

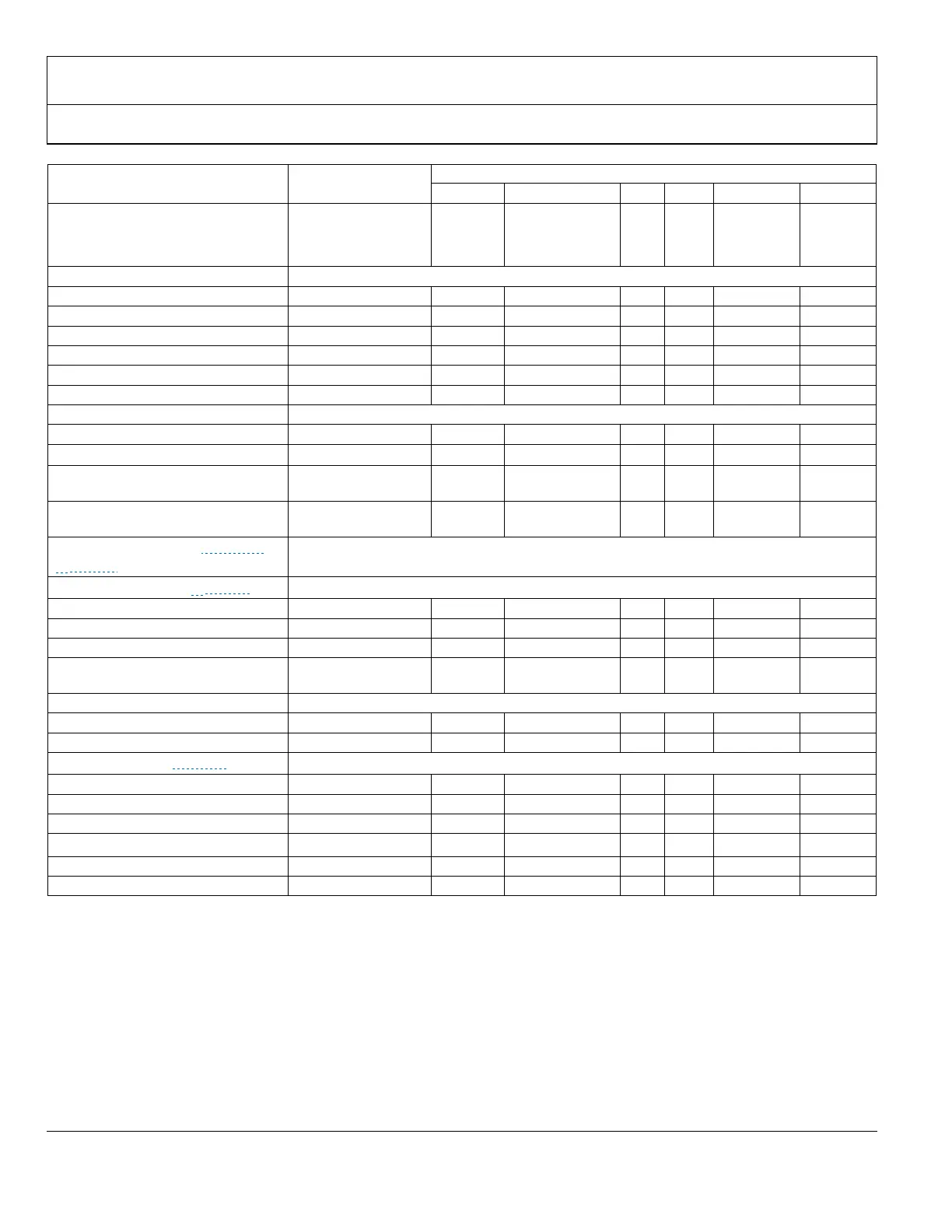

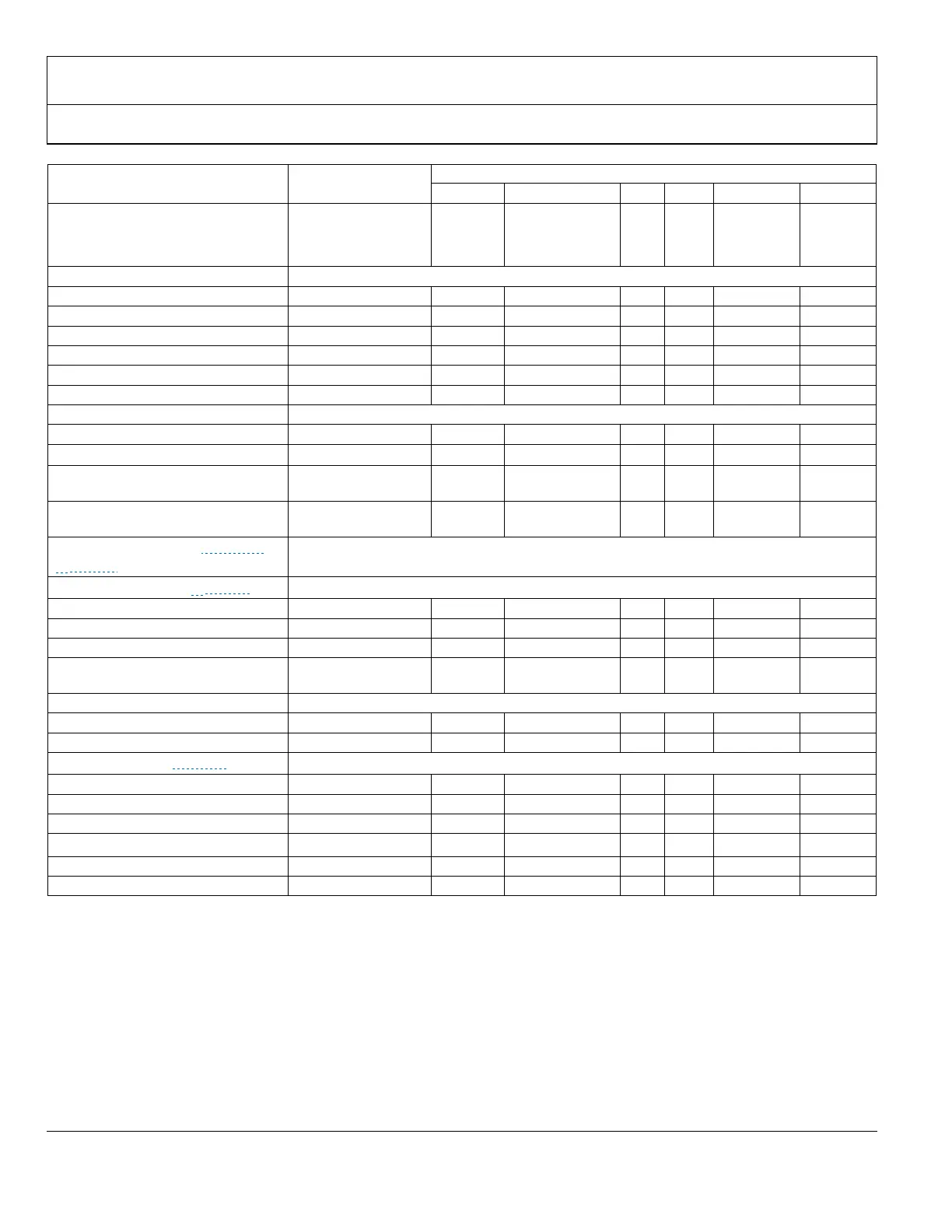

Parameter Conditions

ADV7511W

Temp Test Level

1

Min Typ Max Unit

AC SPECIFICATIONS

TMDS Output Clock Frequency 25°C IV 20 165 MHz

TMDS Output Clock Duty Cycle 25°C IV 48 52 %

Input Video Clock Frequency Full 165 MHz

Input Video Data Setup Time – t

VSU

2

Full IV 1.8 nS

Input Video Data Hold Time – t

VHLD

2

Full IV 1.3 nS

TMDS Differential Swing 25°C VII 900 1100 1200 mV

Differential Output Timing

Low-to-High Transition Time 25°C VII 75 95 pS

High-to-Low Transition Time 25°C VII 75 95 pS

V

SYNC

and H

SYNC

Delay from DE Falling

Edge

25°C IV 1 UI

3

V

SYNC

and H

SYNC

Delay to DE Rising

Edge

25°C IV 1 UI

AUDIO AC TIMING (see ▶ Figure 3 to

▶ Figure 4

SCLK Duty Cycle See ▶ Table 12

When N/2 = even number Full IV 40 50 60 %

When N/2 = odd number Full IV 49 50 51 %

I

2

S[3:0], S/PDIF, LRCLK Setup – t

ASU

Full IV 2 nS

I

2

S[3:0], S/PDIF, LRCLK Hold Time –

t

AHLD

Full IV 2 nS

CEC

CEC_CLK Frequency Full VIII 3 12

4

100 MHz

CEC_CLK Accuracy Full VIII -2 +2 %

I2C Interface (see ▶Figure 19)

SCL Clock Frequency Full 400 kHz

SDA Setup Time - t

DSU

Full 100 nS

SDA Hold Time – t

DHO

Full 100 nS

Setup for Start – t

STASU

Full 0.6 uS

Hold Time for Start – t

STAH

Full 0.6 uS

Setup for Stop – t

STOSU

Full 0.6 uS

1. See Explanation of Test Levels section.

2. This is measured at

0.9V. The relationship between clock and data is programmable in 400ps steps

3. UI = unit interval.

4. 12MHz crystal oscillator for default register settings.

I2C data rates of 100KHz and 400KHz supported.

Loading...

Loading...