ADV7511W HARDWARE USER’S GUIDE

Rev.A

Page 28

of 45

Rev A

6.1.3.2

Inter-IC Sound (I2S) Audio

The ADV7511W can accommodate from two to eight channels of I2S audio at up to a 192KHz sampling rate. The

ADV7511W supports standard I2S, left-justified serial audio, right-justified serial audio and AES3 stream formats via

R0x0C[1:0] and sample word lengths between 16 bits and 24 bits (R0x14[3:0]).

If the I2S data changes on the rising clock edge it is recommended that it be latched into the ADV7511W on the falling

edge. If the I2S data changes on the falling clock edge, it is recommended that it be latched into the ADV7511W on the

rising edge. This can be specified by programming register R0x0B[6]. 0 = latch on the rising clock edge; 1 = latch on

the falling clock edge. For more information see the following figures:

▶

Figure 10 –▶ Figure 13 for format information

▶

Figure 3 for timing information

▷

Please refer to the ADV7511 Programming Guide for more information about configuring the audio.

The accurate transmission of audio depends upon an accurate SCLK and can be a function of the duty cycle of the

SCLK. ▶Table 12

specifies this duty cycle dependency. ‘N’ and ‘CTS’ values are used to reconstruct the audio data and

if the ‘N’ value is an odd number, the SCLK duty cycle must be within the range of 49 – 51%; if the ‘N’ value is an even

number and the audio is in a 32 bit format the SCLK duty cycle requirements can be in a much wider range of 40 –

60%. For the case of 16 bit audio format, ‘N’ values which are not divisible by 4 restrict the duty cycle to 49-51% where

an ‘N’ value which is evenly divisible by 4 may have a duty cycle from 40% - 60%.

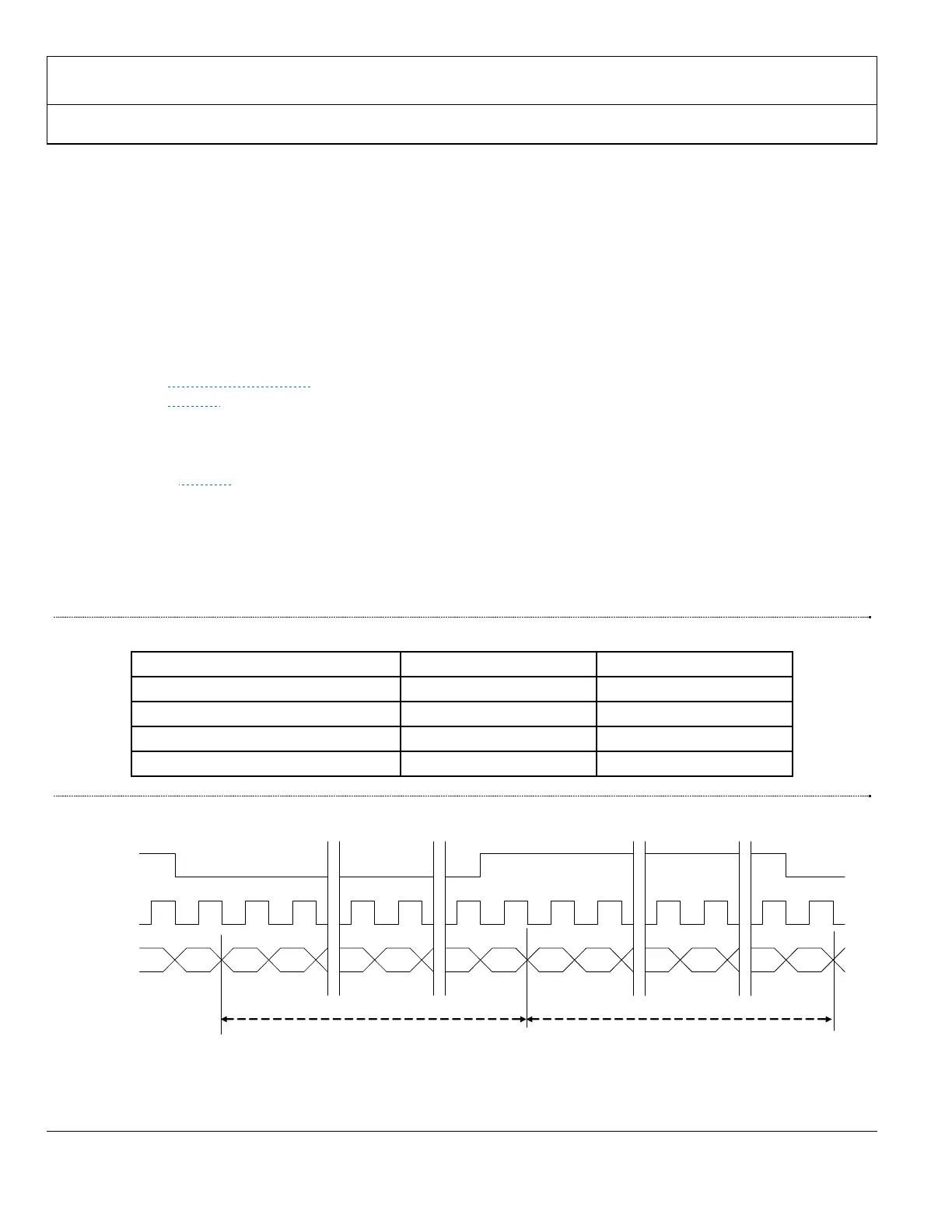

Table 12

SCLK Duty Cycle

SCLK DC requirement SCLK DC requirement

N value 16 bit audio 32 bit audio

N is odd Not supported 49-51%

N is a even but not a multiple of 4 49-51% 40-60%

N is even & a multiple of 4 40-60% 40-60%

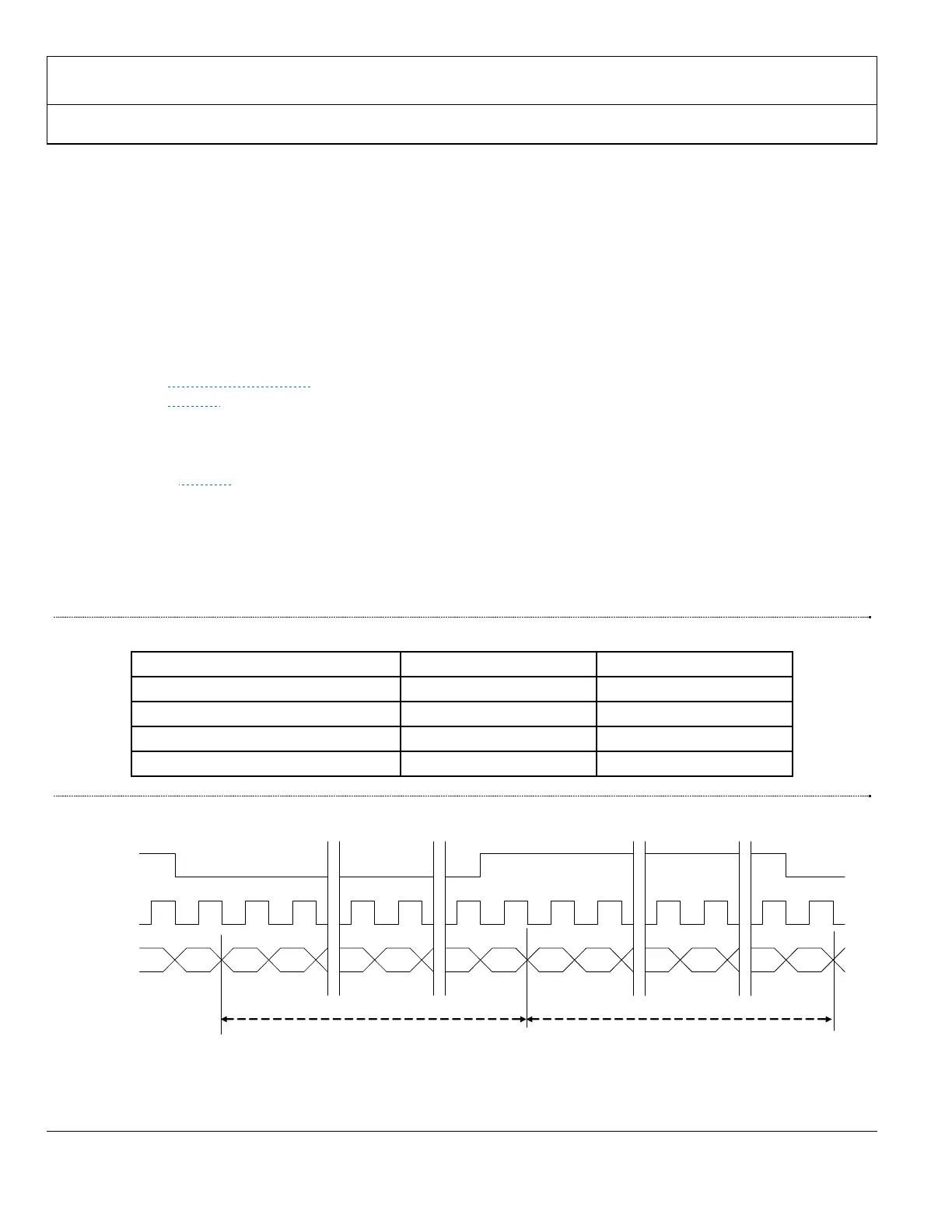

Figure 10 I2S Standard Audio – Data width 16 to 24 bits per channel

LRCLK

SCLK

I2S[3:0]

LEFT RIGHT

LSB

MSB

left

MSB LSB

32 Clock Slots 32 Clock Slots

I2S Standard

R0x0C[1:0] = ‘00’

Loading...

Loading...