ADV7511W HARDWARE USER’S GUIDE

Rev.A

Page 20

of 45

Rev A

SECTION 6: FUNCTIONAL DESCRIPTION

6.1 Input Connections

6.1.1 Unused Inputs

Any input data signals which are not used should be connected to ground.

6.1.2

Video Data Capture Block

The ADV7511W can accept video data from as few as eight pins (either YCbCr 4:2:2 double data rate [DDR] or YCbCr

4:2:2 with 2x pixel clock) to as many as 24 pins (RGB 4:4:4 or YCbCr 4:4:4). In addition it can accept HSYNC, VSYNC

and DE (Data Enable). The ADV7511W can detect all of the 59 video formats defined in the EIA/CEA-861E

specification. Either separate HSYNC, VSYNC, and DE, or embedded syncs in the style of the ITU BT.656, SMPTE

274M, and SMPTE 296M specifications are accepted. The alignment of the data can be defined as left or right justified

or as evenly distribution. In the case of even distribution, the channel data is left-justified in their respective 8-bit

fields. For timing details for video capture, see Figure 2

. For complete details on how to set these, refer to the

ADV7511W Programming Guide.

The ADV7511W can accept HSYNC, VSYNC and DE (Data Enable) signals separately or as an embedded data (ITU

656 based) on the data inputs. If using separate syncs and DE is not available, the DE signal can be generated internally

in the ADV7511W.

The tables in section 6.1.2.1 define how the many different formats are accepted on the

input data lines.

6.1.2.1

Video Input Connections

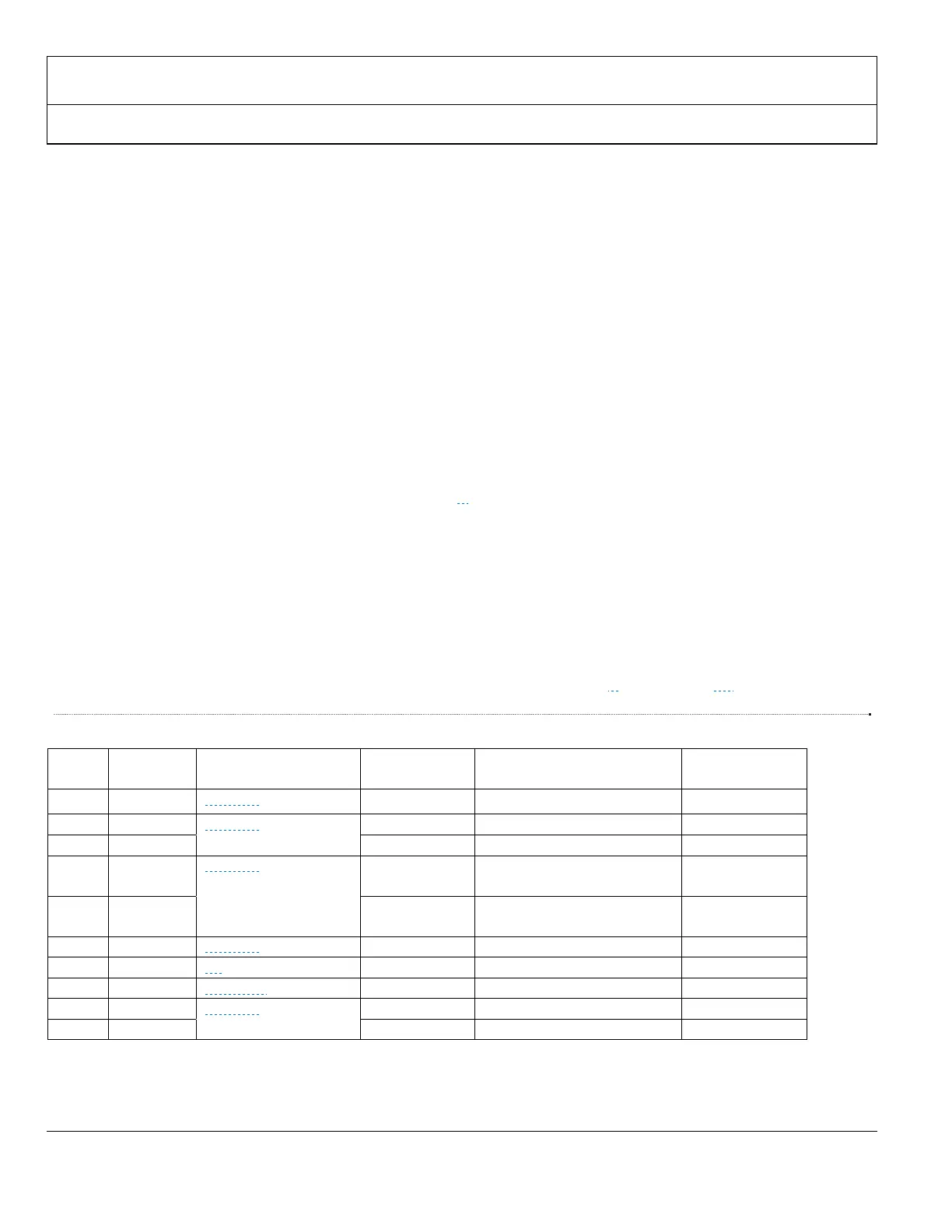

The following table is a summary of the input options which are shown in detail in Table 5 through Table 10.

Table 4

Input ID Selection

Input

ID

Bits per

Color

Pin Assignment Table Maximum

Input Clock

Format Name Sync Type

0 8 ▶Table 5 165.0 MHz RGB 4:4:4, YCbCr 4:4:4 Separate syncs

1 8, 10, 12 ▶Table 6

165.0 MHz YCbCr 4:2:2 (even dist.) Separate syncs

2 8, 10, 12 165.0 MHz YCbCr 4:2:2 (even dist.) Embedded syncs

3 8, 10, 12 ▶Table 7 82.5 MHz YCbCr 4:2:2 2X cloc

(even

dist.)

Separate syncs

4 8, 10, 12 82.5 MHz YCbCr 4:2:2 2X cloc

(even

dist.)

Embedded syncs

6 8 ▶Table 8 82.5 MHz YCbCr 4:2:2 DD

(right just.) Separate syncs

6 8 ▶0 82.5 MHz YCbCr 4:2:2 DDR (left just.) Separate syncs

6 8, 10, 12 ▶Table 10 82.5 MHz YCbCr 4:2:2 DDR (even dist.) Separate syncs

7 8, 10, 12 ▶Table 7 82.5 MHz YCbCr 4:2:2 DDR (even dist.) Separate syncs

8 8, 10, 12 82.5 MHz YCbCr 4:2:2 DD

(even dist.) Embedded syncs

Loading...

Loading...