54

ATtiny26(L)

1477G–AVR–03/05

• DI/SDA/OC1A/PCINT0 – Port B, Bit 0

DI: Data Input in USI Three-wire mode. USI Three-wire mode does not override normal

port functions., so pin must be configure as an input.

SDA: Serial Data in USI Two-wire mode. Serial data pin is bi-directional and uses open-

collector output. The SDA pin is enabled by setting the pin as an output. The pin is

pulled low when the PORTB0 or USI shiftRegister is zero when DDB0 is set (one). Pull-

up is disabled in USI Two-wire mode.

OC1A

: Inverted Timer/Counter1 PWM output A: The PB0 pin can serve as an Inverted

output for the PWM mode if not used in programming or USI. The PB0 pin has to be

configured as an output (DDB0 set (one)) to serve this function.

PCINT0: Pin Change Interrupt 0 pin. Pin change interrupt is enabled on pin when global

interrupt is enabled, pin change interrupt is enabled and the alternate functions do not

mask the interrupt. The masking alternate functions are the inverted output compare

match output OC1A

and USI data DI or SDA. Digital input is enabled on pin PB0 also in

SLEEP modes, if the pin change interrupt is enabled and not masked by the alternate

functions. Table 27 and Table 28 relate the alternate functions of Port B to the overriding

signals shown in “Alternate Port Functions” on page 46.

Notes: 1. RSTDISBL Fuse (active low) is described in section “System Control and Reset” on page 31.

2. Note that the PCINT1 Interrupt is only enabled if both the Global Interrupt Flag is enabled, the PCIE1 flag in GIMSK is set

and the alternate function of the pin is disabled as described in “Pin Change Interrupt” on page 62.

3. PB5IOENABLE and PB4IOENABLE are given by the PLLCK and CKSEL Fuses as described in “Clock Sources” on page

24.

4. External low level interrupt is enabled if both the Global Interrupt Flag is enabled and the INT0 flag in GIMSK is set as

described in “External Interrupt” on page 62.

5. Not operator is marked with “~”.

6. The operation of the Timer/Counter0 with external clock disabled is described in “8-bit Timer/Counter0” on page 65.

7. External clock is selected by the PLLCK and CKSEL Fuses as described in “Clock Sources” on page 24.

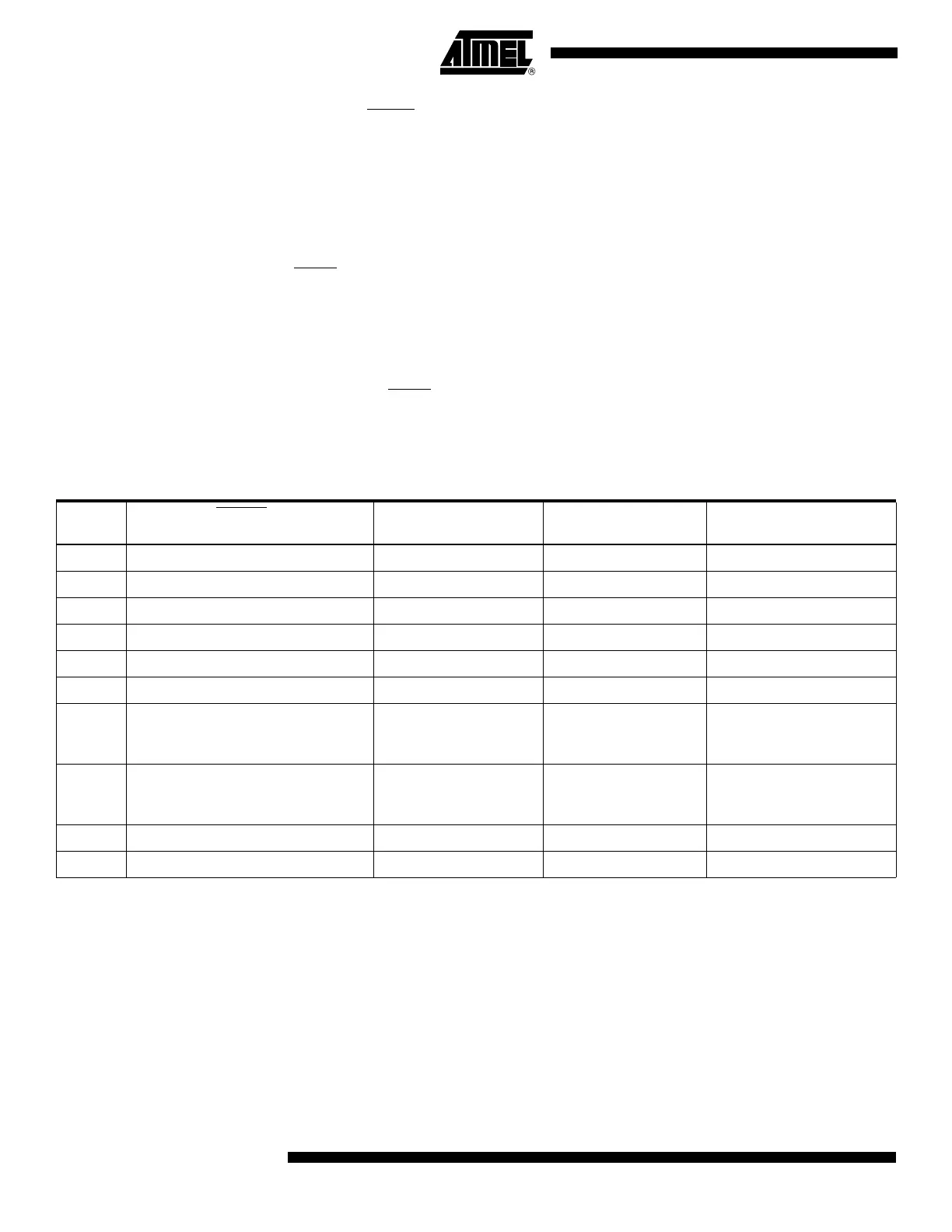

Table 27. Overriding Signals for Alternate Functions in PB7..PB4

Signal

Name

PB7/ADC10/RESET/

PCINT1

PB6/ADC9/INT0/TO/

PCINT1

PB5/ADC8/XTAL2/

PCINT1 PB4/ADC7/XTAL1

PUOE RSTDSBL

(1)

0~

(5)

PB5IOENABLE

(3)

~PB4IOENABLE

(3)

PUOV 1 0 0 0

DDOE RSTDSBL

(1)

0 ~PB5IOENABLE

(3)

~PB4IOENABLE

(3)

DDOV 0 0 0 0

PVOE 0 0 0 0

PVOV 0 0 0 0

DIEOE PCINT1_ENABLE

(2)

| RSTDSBL

(1)

~T0_EXT_CLOCK

(6)

•

PCINT1_ENABLE

(2)

|

INT0_ENABLE

(4)

PCINT1_ENABLE

(2)

|

~PB5IOENABLE

(3)

PCINT_ ENABLE

(2)

|

~PB4IOENABLE

(3)

|

EXT_CLOCK_ENABLE

(7)

DIEOV PCINT1_ENABLE

(2)

•

~

(5)

RSTDSBL

(1)

1 PCINT1_ENABLE

(2)

•

PB5IOENABLE

(3)

PCINT1_ENABLE

(2)

•

PB4IOENABLE

(3)

|

EXT_CLOCK_ENABLE

DI PCINT1 INT0, T0, PCINT1 PCINT1 External Clock, PCINT1

AIO ADC10, RESET INPUT ADC9 ADC8, XTAL2 XTAL1

Loading...

Loading...