Chapter 6 Applied Instructions

6-283

API

Instruction code

Operand Function

1211 MINV P

S, D, n

Inverting the matrix bits

Device

X Y M S T C HC D L SM SR E PR K 16# “$” DF

16-bit instruction (7 steps)

Symbol:

S

:

Matrix source Word

D

:

Operation result Word

n

:

Length of the array Word

Explanation:

1. The bits in the n devices starting from the device specified by S are inverted, and the inversion

result is stored in D.

2. The operand n should be within the range between 1 and 256.

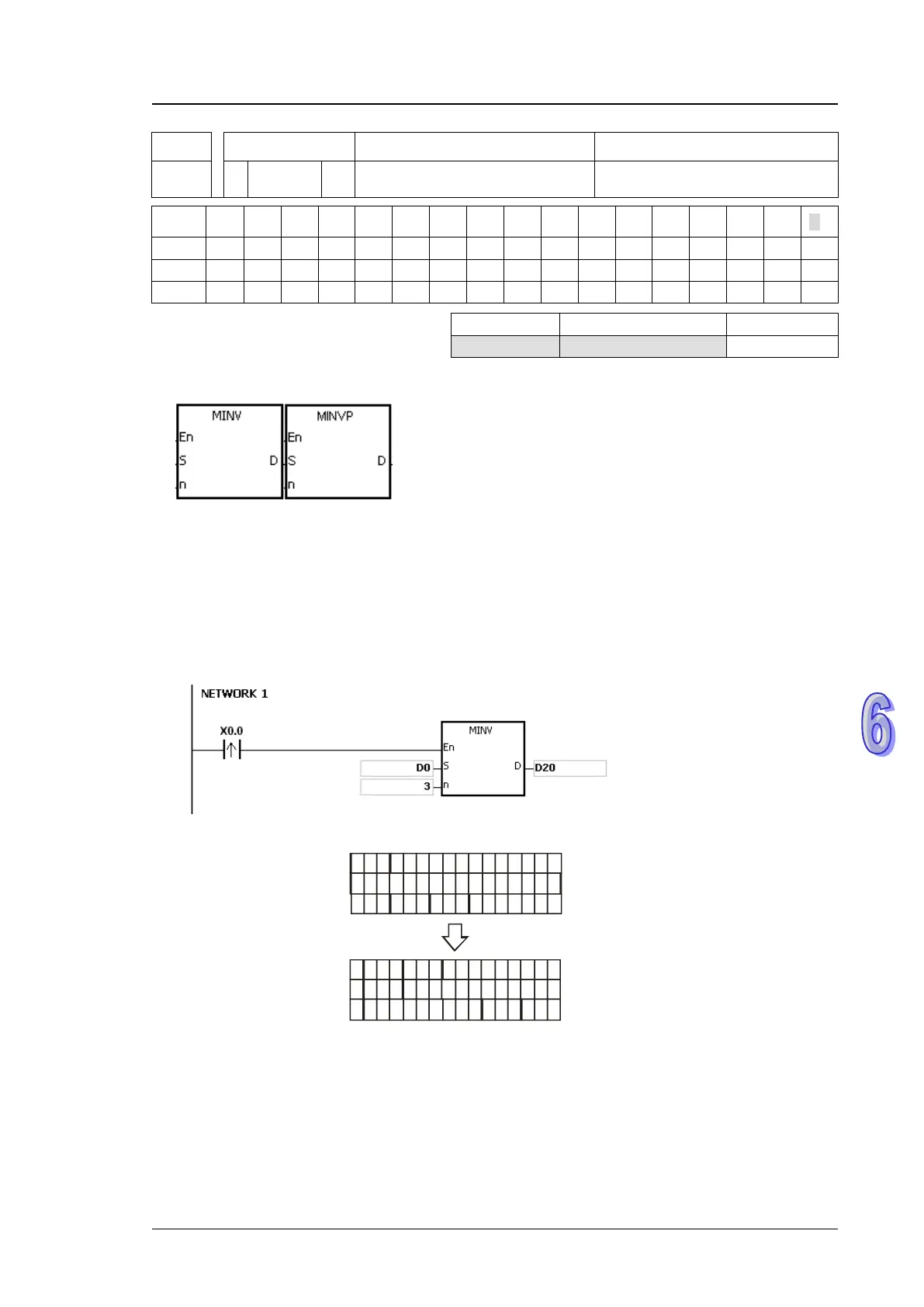

Example:

When X0.0 is ON, the bits in the three 16-bit registers D0~D2 are inverted, and the inversion result

is stored in the 16-bit registers D20~D22.

0 1 0 1 0 1 0 1 0 1

0 1 0 1

0 1

b0

b15

0 1 0 1 0 1 0 1 0 1

0 1 0 1

0 1

0 1 0 1 0 1 0 1 0 1

0 1 0 1

0 1

0 1 0 1 0 1 0 1 0 1

0 1 0 1

01

b0

b15

0 1 0 1 0 1 0 1 0 1

0 1 0 1

01

0 1 0 1 0 1 0 1 0 1

0 1 0 1

01

D0

D1

D2

D20

D21

D22

After the instruction is executed

Additional remark:

1. If S+n-1 or D+n-1 exceeds the device range, the instruction is not execute, SM0 is ON, and

the error code in SR0 is 16#2003.

2. If n is less than 1, or if n is larger than 256, the instruction is not executed, SM0 is ON, and the

error code in SR0 is 16#200B.

Loading...

Loading...