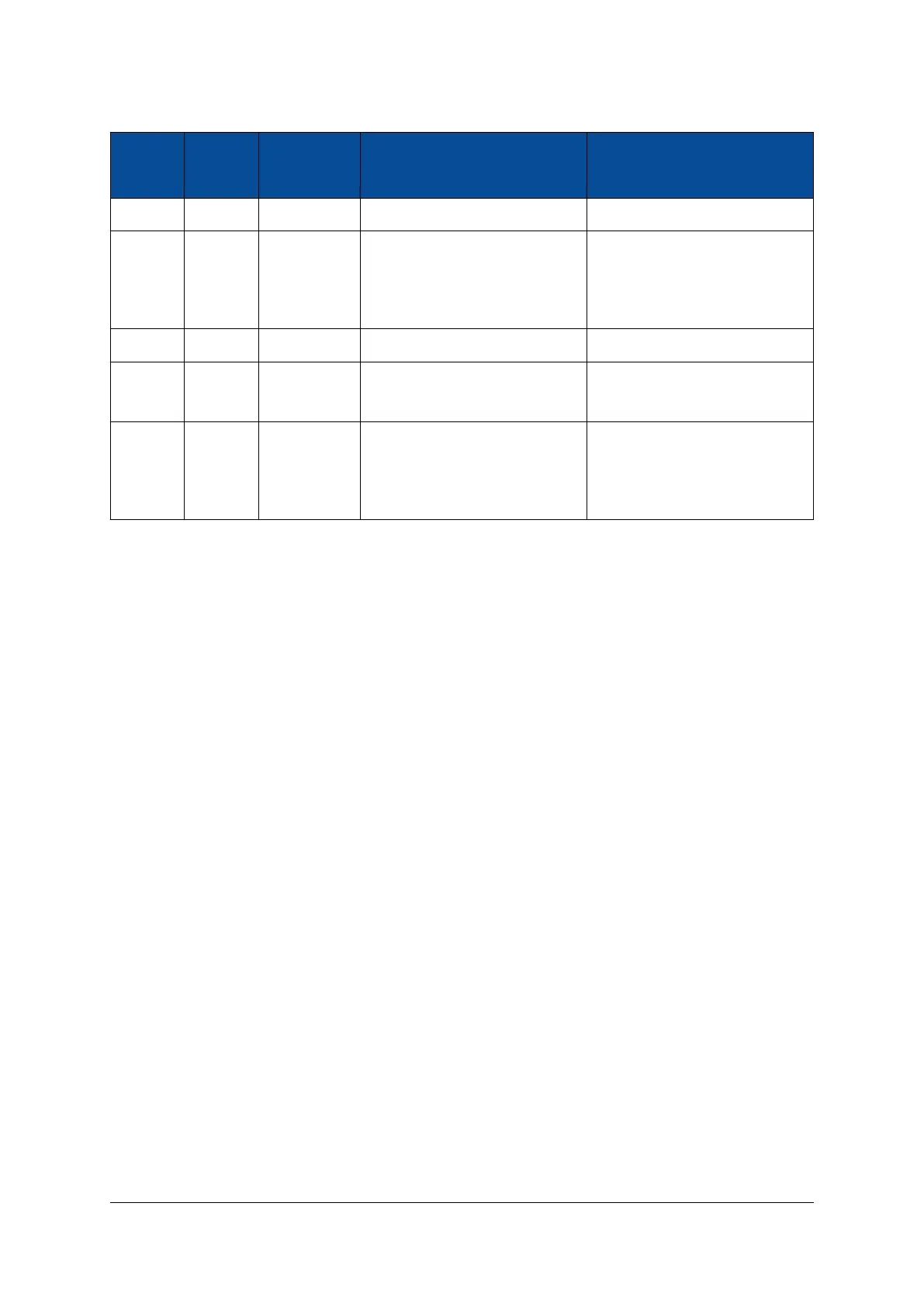

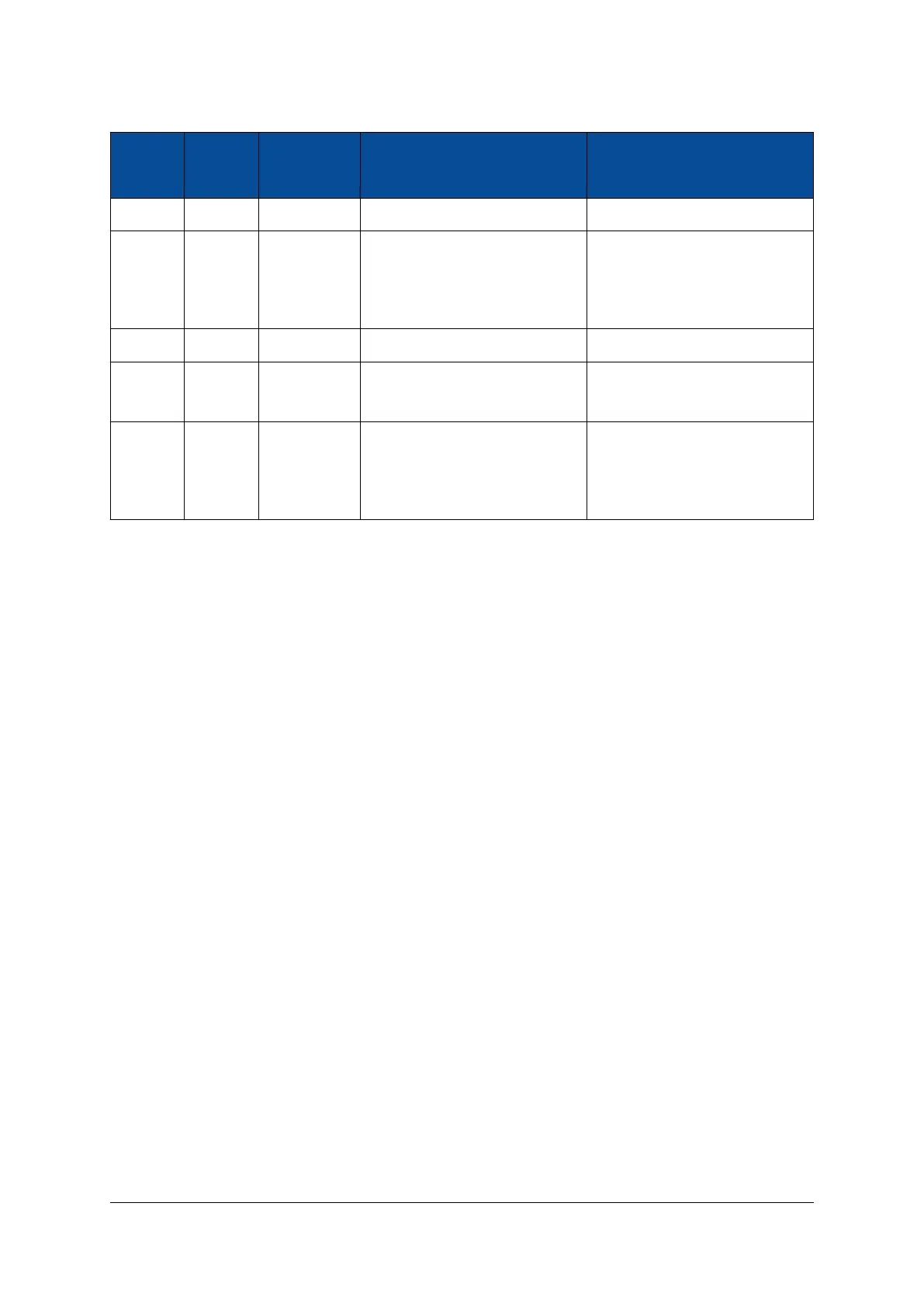

BOOT BOOT Mode Description Remarks

MODE1 MODE0 Straps [3:0]

0 0 0110 Boot from eMMC flash -

0 1 1110 Boot from SD card (with an ex-

ternal SD 3.0 compliant level

shifter; only available when

VCC_CFG_MIO is 1.8 V)

Not supported (may be sup-

ported in the future)

1 0 0010 Boot from QSPI flash -

1 1 0101 Boot from SD card (default

mode)

-

1 0 0000 JTAG boot mode Available only starting with re-

vision 2 modules in certain con-

ditions (refer to Section 3.6.3 for

details).

Table 37: Boot Modes

3.6 JTAG

The Zynq Ultrascale+ devices include two separate JTAG controllers: the Zynq Ultrascale+ TAP and the ARM

DAP. The first one uses the PS dedicated JTAG pins and has access to both PS and PL and the second one

uses the PS PJTAG pins and is used for loading programs, system test, and PS debug.

Details on JTAG and on system test and debug are available in the Zynq UltraScale+ MPSoC Technical Ref-

erence Manual [18].

Certain Xilinx tool versions support QSPI flash programming via JTAG only when JTAG boot mode is used.

Alternatively, the QSPI flash can be programmed in u-boot or Linux by the SPI controller in the PS or from

an SPI external master.

3.6.1 JTAG on Module Connector

The PL and the PS JTAG interfaces are connected into one single chain available on the module connector.

The PS_JTAG pins are used by the Zynq Ultrascale+ TAP controller - the controller has full functionality only

after the PS boot is complete. In order to enable the ARM DAP controller, special commands must be sent

to the Zynq Ultrascale+ TAP.

The MPSoC device and the flash devices can be configured via JTAG from Xilinx SDK or Xilinx Vivado Hard-

ware Manager - for this operation, the ARM DAP must be enabled.

D-0000-454-001 47 / 60 Version 06, 18.11.2019

Loading...

Loading...