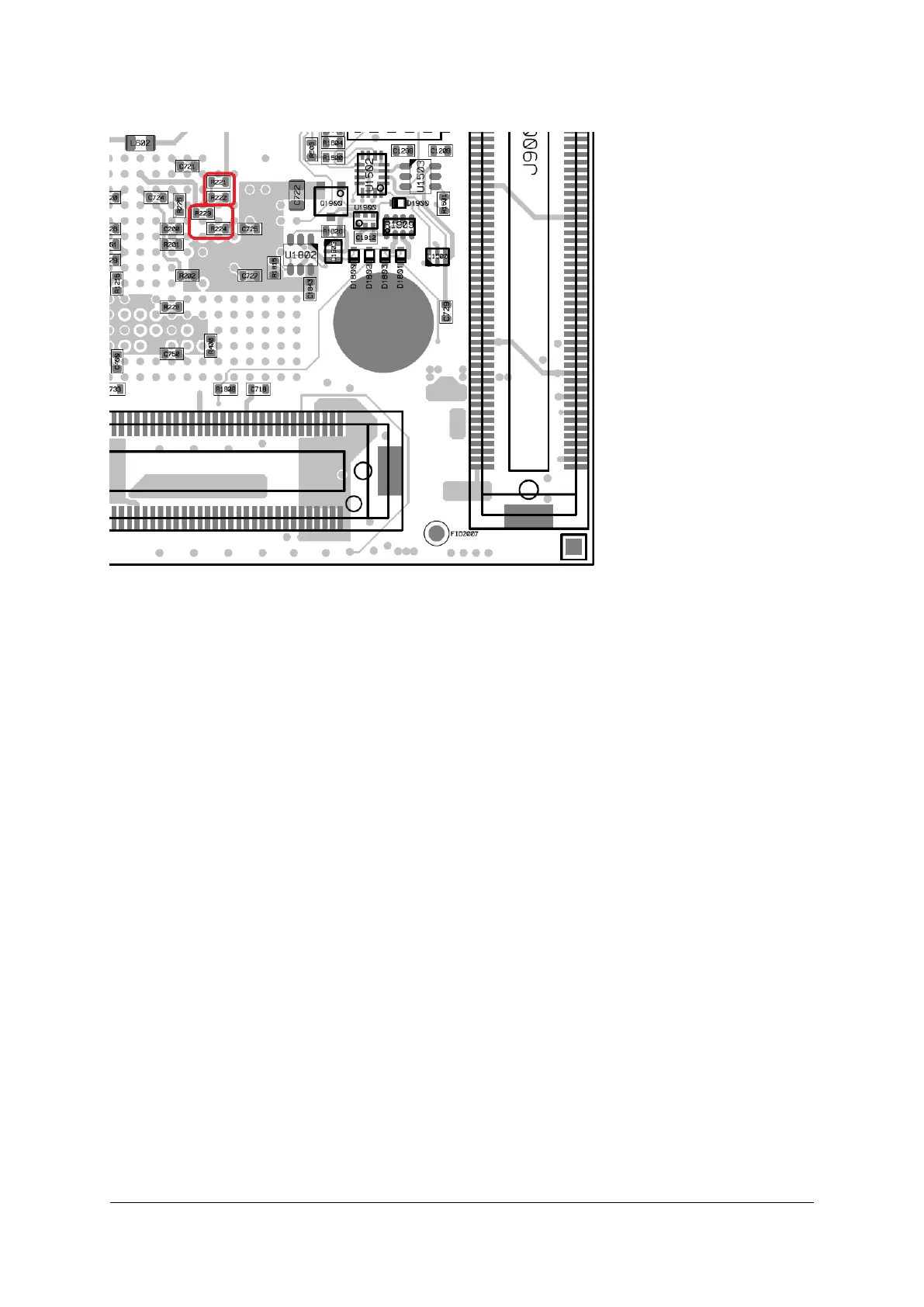

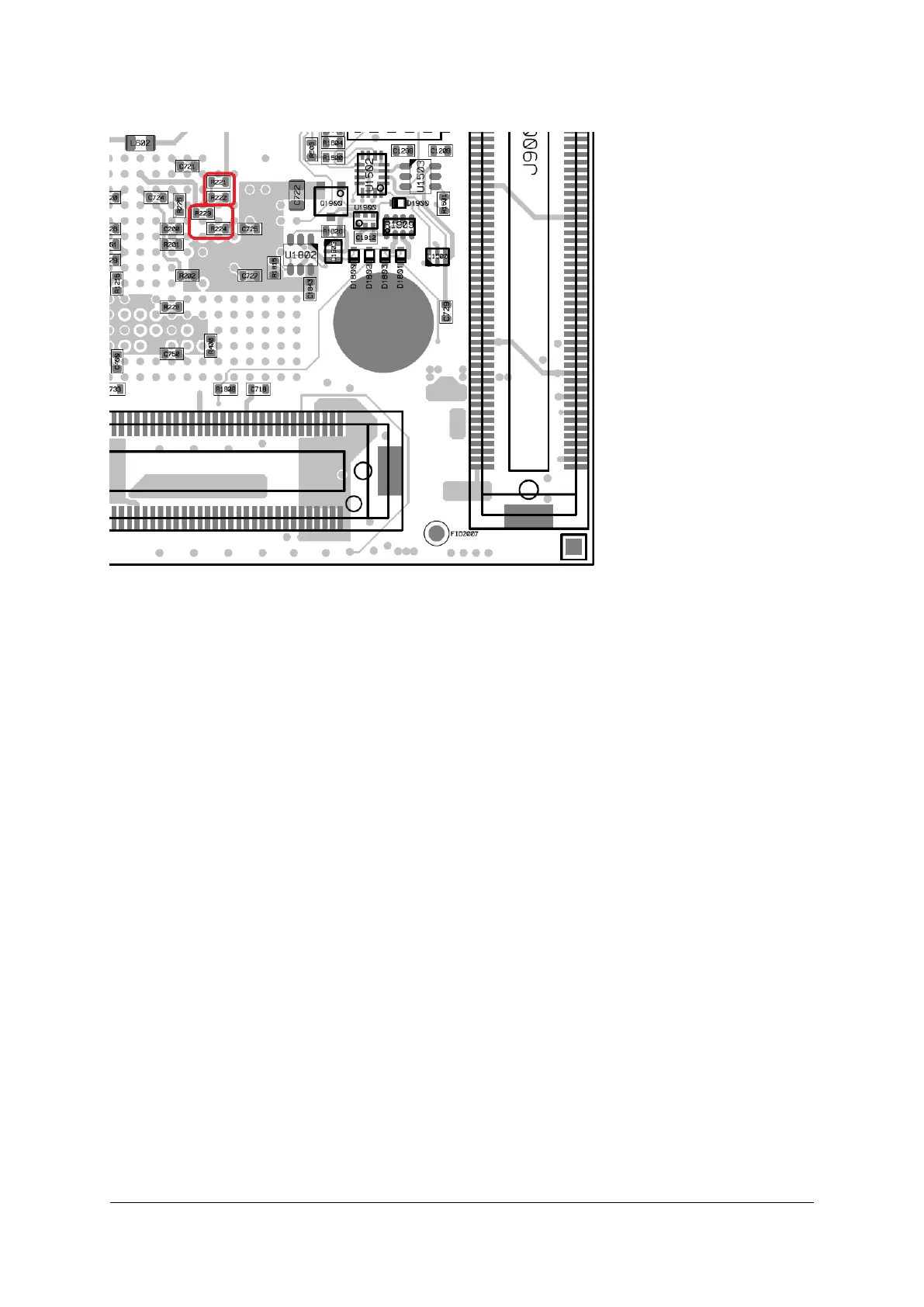

Figure 13: Pull-Up During Configuration (PUDC) and Power-on Reset Delay Override (PORSEL) Resistors - Assembly

Drawing Bottom View (lower right part)

For details on the PUDC signal please refer to the Zynq UltraScale+ MPSoC Technical Reference Manual

[18].

3.4 Power-on Reset Delay Override

The power-on reset delay override MPSoC signal (POR_OVERRIDE) is pulled to GND on the module, setting

the PL power-on delay time to the default standard time.

If the application requires faster PL power-on delay time, this can be achieved by removing R224 component

and by mounting R223.

Figure 12 illustrates the configuration of the POR_OVERRIDE signal. Figure 13 indicates the location of the

pull-up/pull-down resistors on the module PCB - lower right part on the bottom view drawing.

For details on the POR_OVERRIDE signal please refer to the Zynq UltraScale+ MPSoC Technical Reference

Manual [18].

3.5 Boot Mode

The boot mode can be selected via two signals available on the module connector.

Table 37 describes the available boot modes on the Mercury+ XU8 SoC module.

Starting with revision 2, JTAG boot mode has been introduced to increase the usability with Xilinx tools,

which may report issues when programming the on-board QSPI flash or when loading the FPGA bitstream

in a non-JTAG boot mode.

D-0000-454-001 46 / 60 Version 06, 18.11.2019

Loading...

Loading...