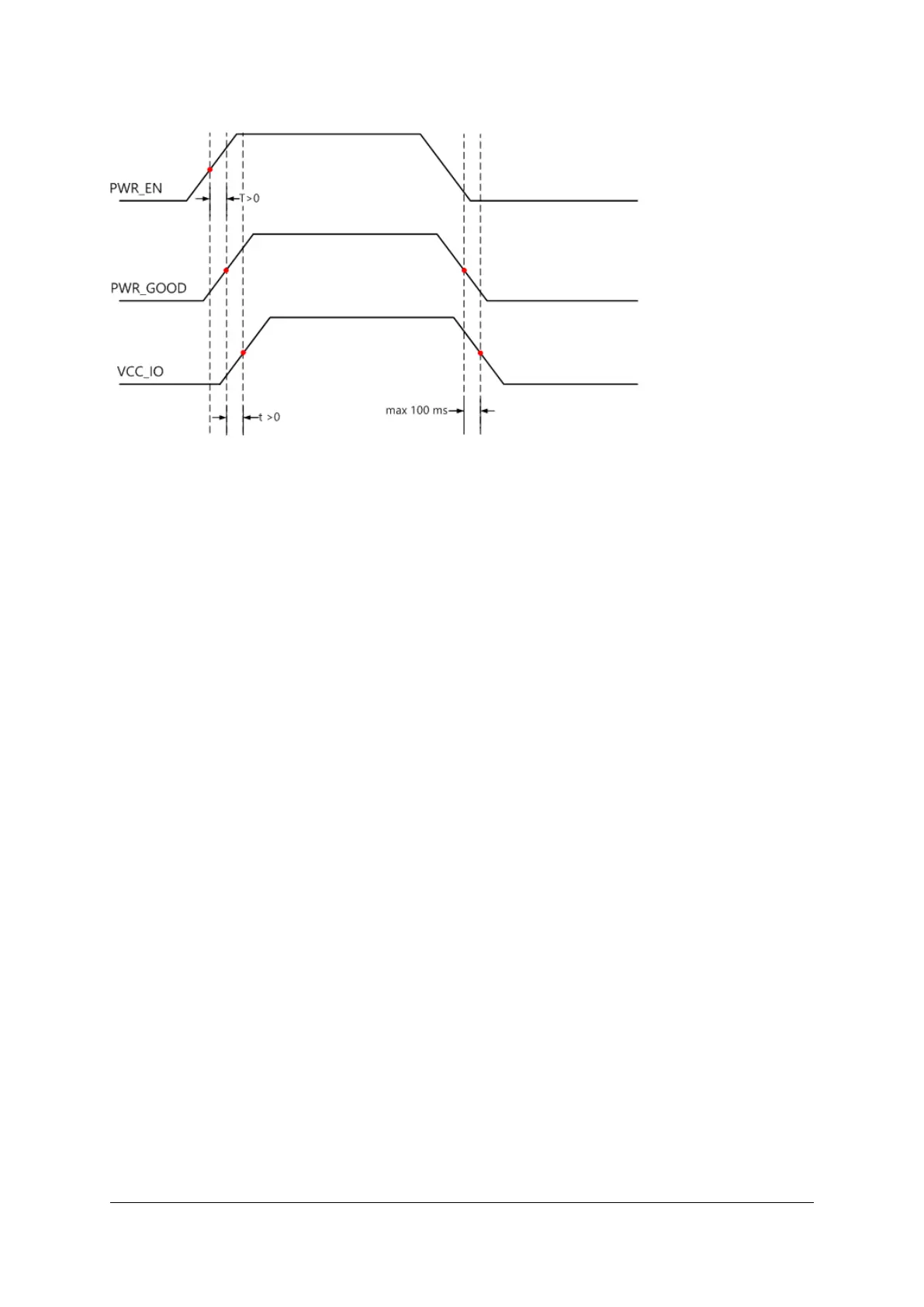

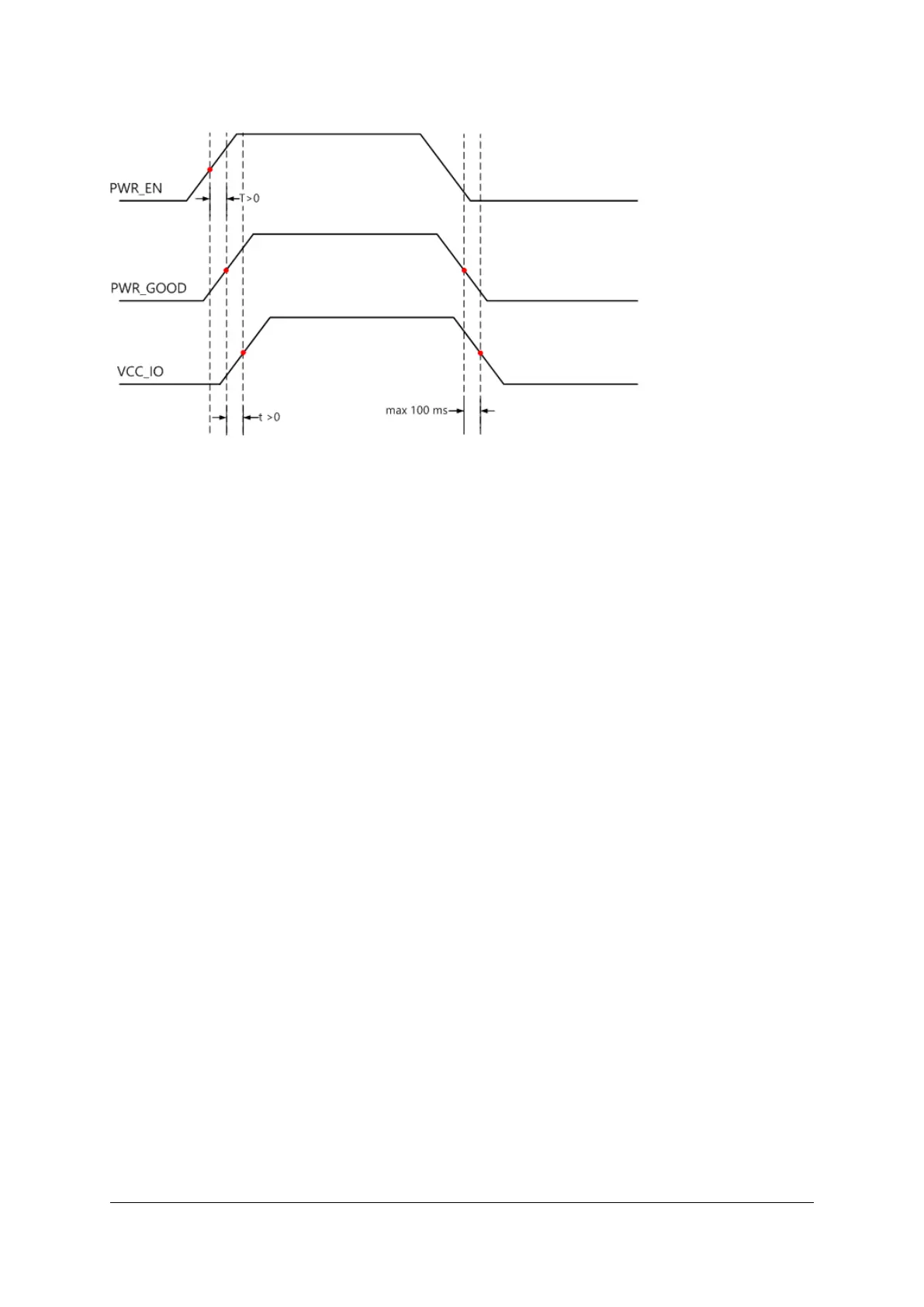

Figure 10: Power-Up Sequence - VCC_IO in Relation with PWR_GOOD and PWR_EN Signals

2.9.6 Signal Terminations

Differential Inputs

Internal differential termination is not supported for the HD pins (banks 46, 45 on ZU4/ZU5 devices, and

banks 47, 48 on ZU7 devices). All differential signal pairs from both HD banks may optionally be equipped

with 100 Ω differential termination resistors on the module.

The resistor identifiers for each differential input pair can be retrieved from the Mercury+ XU8 SoC Module

User Schematics [5].

Single-Ended Outputs

There are no series termination resistors on the Mercury+ XU8 SoC module for single-ended outputs. If

required, series termination resistors may be equipped on the base board (close to the module pins).

2.9.7 Multiplexed I/O (MIO) Pins

Details on the MIO/EMIO terminology are available in the Zynq UltraScale+ MPSoC Technical Reference

Manual [18].

Some of the MIO pins on the Mercury+ XU8 SoC module are connected to on-board peripherals, while

others are available as GPIOs; the suggested functions below are for reference only - always verify your MIO

pinout with the Xilinx device handbook.

Table 10 gives an overview over the MIO pin connections on the Mercury+ XU8 SoC module. Only the pins

marked with “user functionality” are available on the module connector.

D-0000-454-001 22 / 60 Version 06, 18.11.2019

Loading...

Loading...