PS Signal Name PS Signal Location Remarks

PS_ERROR R22 (PS_ERROR_OUT) Refer to Zynq UltraScale+ MPSoC Technical Reference

Manual [18]

PS_STATUS R20 (PS_ERROR_STATUS) Refer to Zynq UltraScale+ MPSoC Technical Reference

Manual [18]

Table 23: Status LEDs

2.15 DDR4 SDRAM (PS)

There are two DDR4 SDRAM channels on the Mercury+ XU8 SoC module: one attached directly to the PS

side (which is available only as a shared resource to the PL side) and one attached directly to the PL side.

The DDR4 SDRAM connected to the PS is mapped to I/O bank 504. The memory configuration on the

Mercury+ XU8 SoC module supports ECC error detection and correction; the correction code type used is

single bit error correction and double bit error detection (SEC-DED).

Five 16-bit memory chips are used to build an 72-bit wide memory (8 bits are unused): 64 bits for data and

8 bits for ECC.

The maximum memory bandwidth on the Mercury+ XU8 SoC module is:

2400 Mbit/sec × 64 bit = 19200 MB/sec

2.15.1 DDR4 SDRAM Type

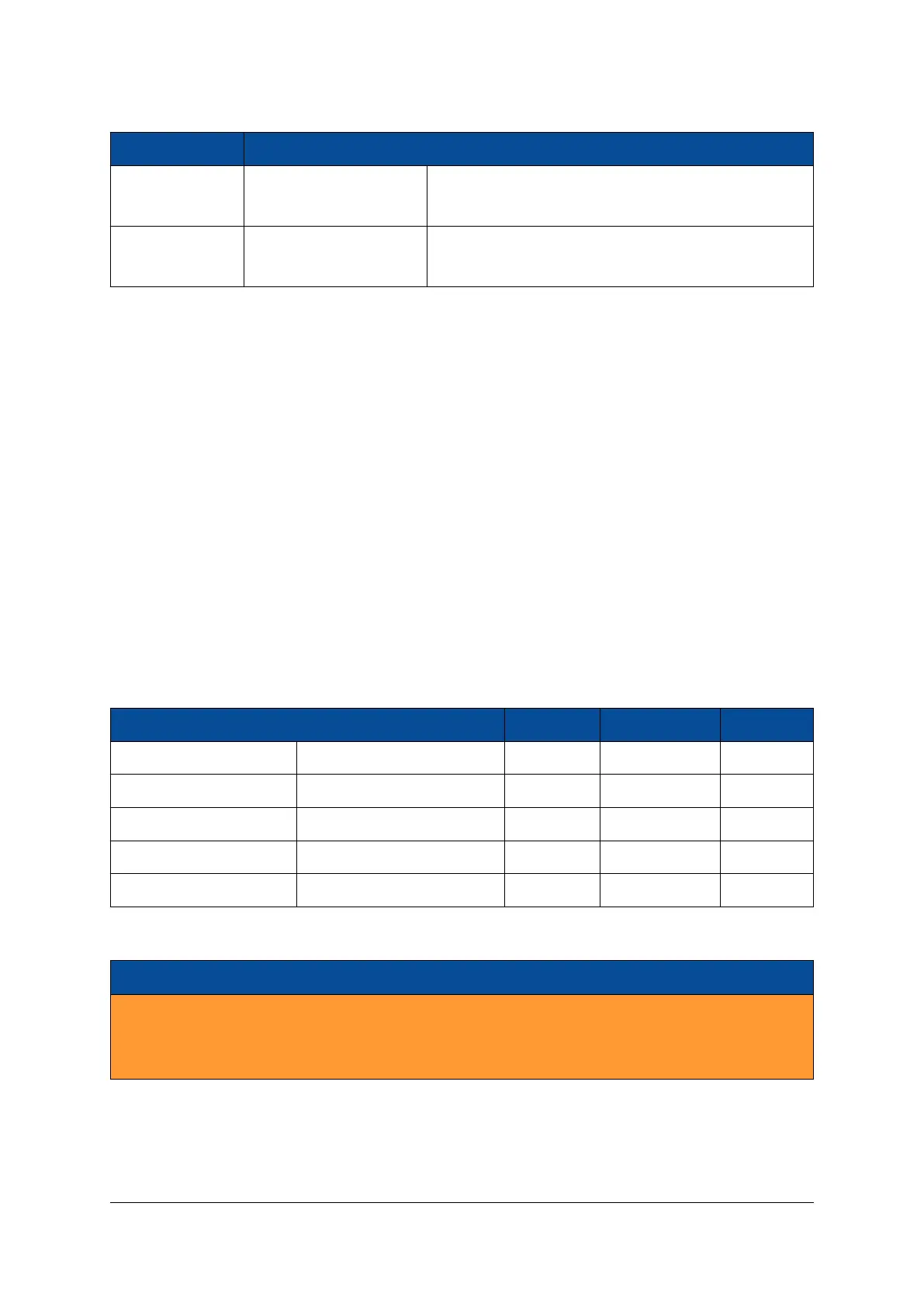

Table 24 describes the memory availability and configuration on the Mercury+ XU8 SoC module.

Module SDRAM Type Density Configuration Manufact.

ME-XU8-D11E (extended) MT40A256M16GE-083E 4 Gbit 256 M × 16 bit Micron

ME-XU8-D11E (extended) H5AN4G6NAFR-UHC 4 Gbit 256 M × 16 bit SK Hynix

ME-XU8-D11E (industrial) MT40A256M16GE-083E-IT-B 4 Gbit 256 M × 16 bit Micron

ME-XU8-D11E (industrial) K4A4G165WE-BIRC 4 Gbit 256 M × 16 bit Samsung

ME-XU8-D12E (industrial) K4A8G165WB-BIRC 8 Gbit 512 M × 16 bit Samsung

Table 24: DDR4 SDRAM (PS) Types

Warning!

Other DDR4 memory devices may be equipped in future revisions of the Mercury+ XU8 SoC module.

Please check the user manual regularly for updates. Any parts with different speed bins or temperature

ranges that fulfill the requirements for the module variant may be used.

D-0000-454-001 33 / 60 Version 06, 18.11.2019

Loading...

Loading...