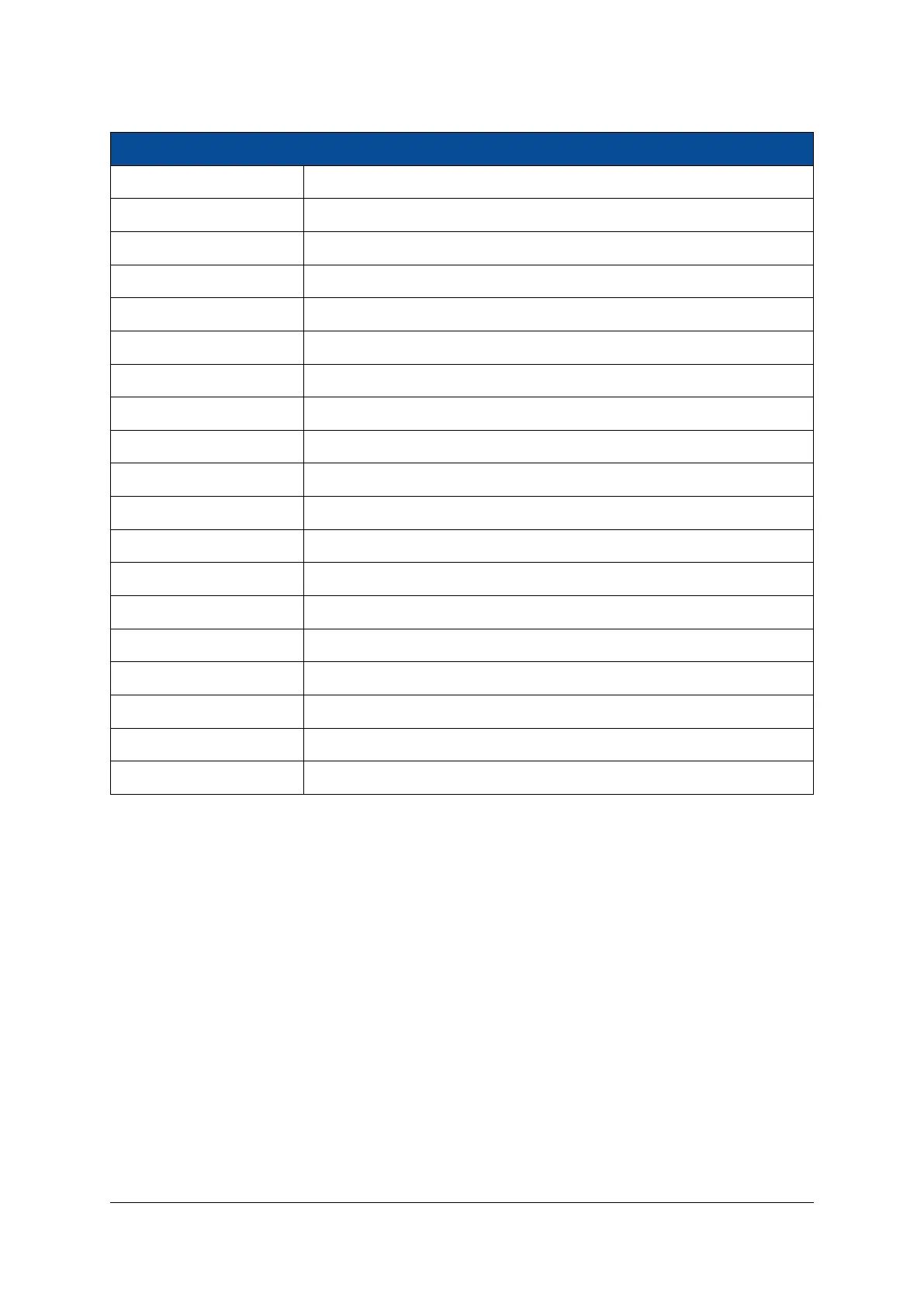

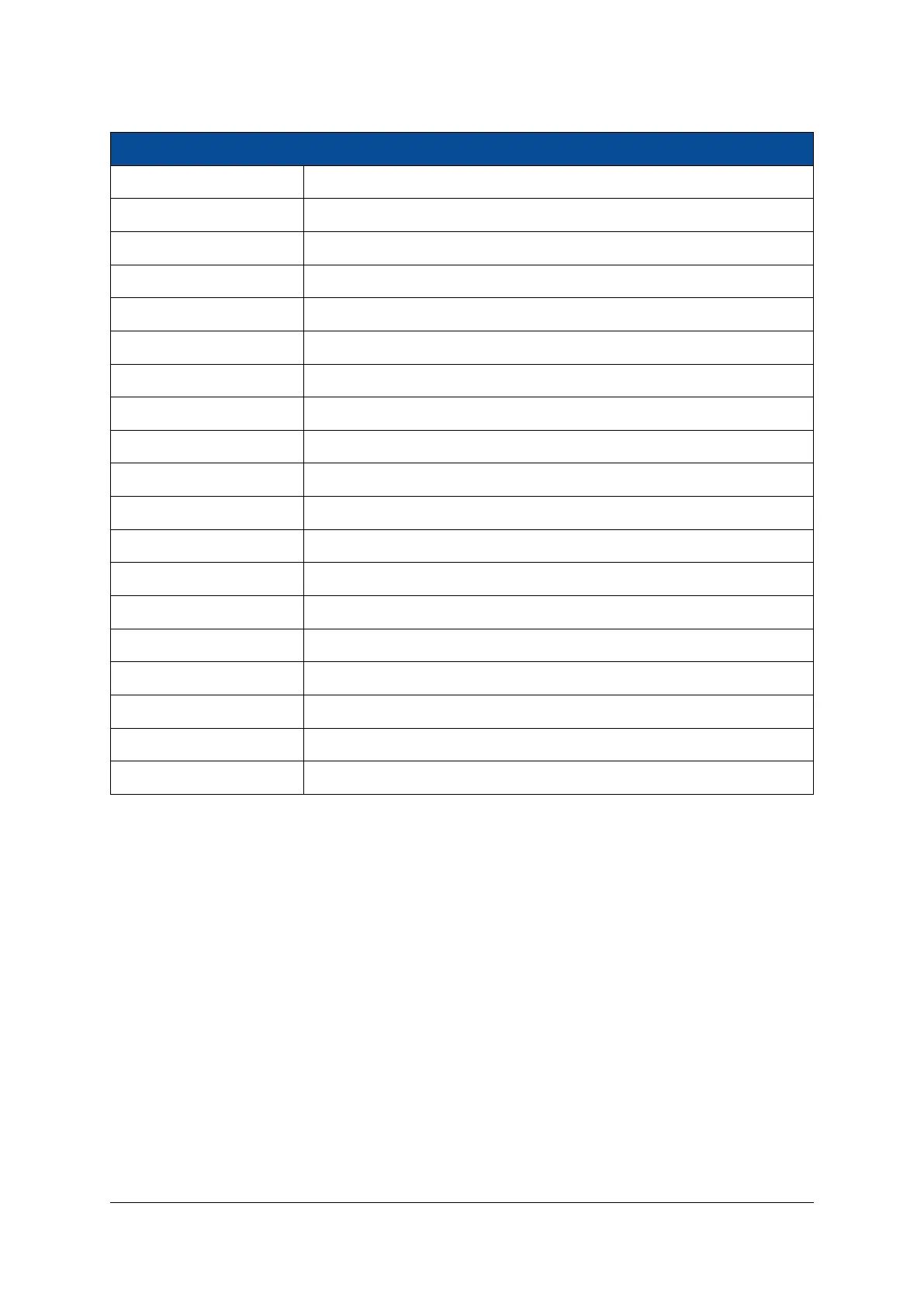

Parameter Value

Memory type DDR4

DRAM bus width 64 bit

ECC Enabled

DRAM chip bus width 16 bits

DRAM chip capacity 4096-8192 Mbits

Bank group address count 1

Bank address count 2

Row address count 15-16

Column address count 10

Speed bin DDR4 2400T

Operating frequency 1200 MHz

CAS latency 17

CAS write latency 12

Additive latency 0

RAS to CAS delay 17

Precharge time 17

tRC 46.16 ns

tRASmin 32 ns

tFAW 30 ns

Table 25: DDR4 SDRAM (PS) Parameters

2.16 DDR4 SDRAM (PL)

The DDR4 SDRAM connected to the PL is mapped to I/O banks 64 and 65. The DDR bus width is 32-bit.

The DDR4 SDRAM memory controller on the MPSoC device supports speeds up to 2666 Mbit/s (1333 MHz),

however the memories equipped on the Mercury+ XU8 SoC module are rated 2400 Mbit/s (1200 MHz).

The maximum PL memory bandwidth on the Mercury+ XU8 SoC module is:

2400 Mbit/sec × 32 bit = 9600 MB/sec

Note that for MPSoC low power mode (at 0.72 V) the DDR speed is lower than mentioned above. For details,

refer to the Zynq UltraScale+ MPSoC, DC and AC Switching Characteristics [20].

D-0000-454-001 35 / 60 Version 06, 18.11.2019

Loading...

Loading...