Maintenance

Troubleshooting

4

4-27

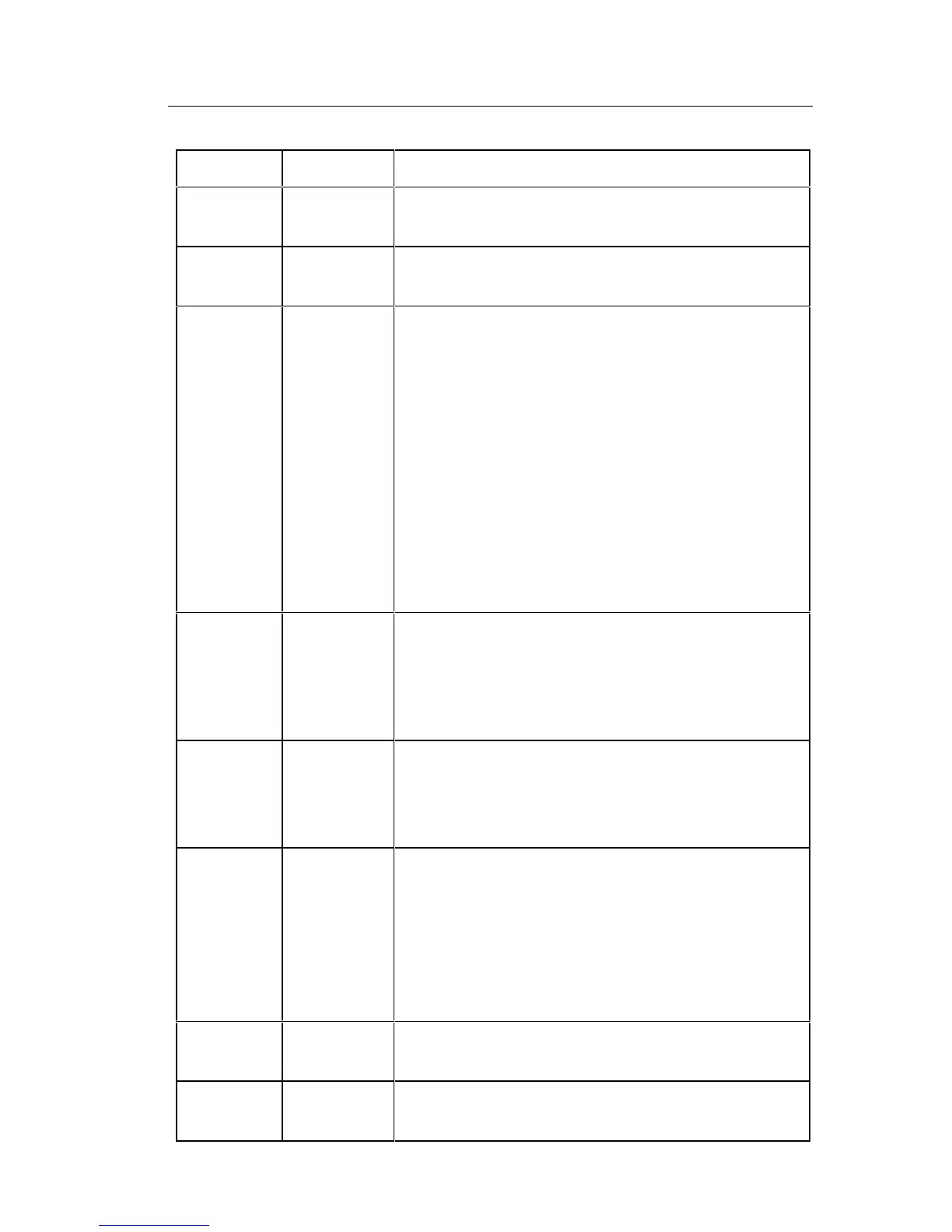

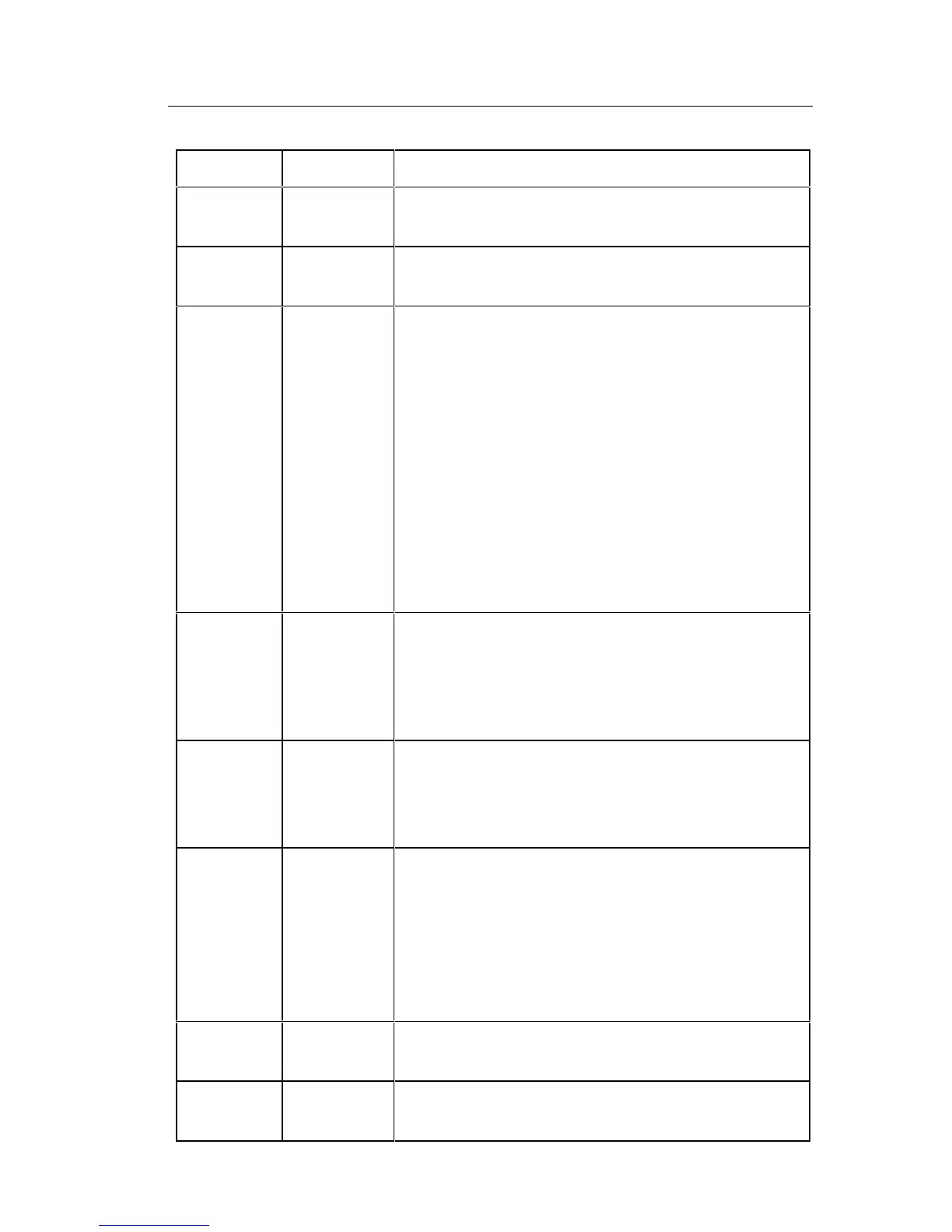

Table 4-8. U3 (MAC) Pin Descriptions (cont)

Pin No. Mnemonic Description

12

13

OREF-

OREF+

Reference input to a/d converter during

autozero period for resistance functions.

14

15

BFH

BFL

Output of the a/d buffer circuit.

16

17

18

19

20

21

22

23

AZ

INT

BTI

VIA

CV

VDD

VID

VDG

Input for AZ capacitor.

Input for INTEG capacitor.

Battery test input.

+5.2V supply feedback (nominally 1V)

Gate drive for JFET. Series pass element

+5.2V supply.

Reference voltage for the U3 and U5 digital

power supply.

Output of the U3 and U5 digital power supply.

24

25

26

27

AD0

AD1

AD2

AD3

Four-bit parallel data bus between U3 and U5.

During the first part of a data transfer operation

they carry the address of the register being

read or written to. During the remainder of the

operation they carry data.

28

29

30

WR/

ALE/

RD/

Register write strobe.

Address Latch Enable.

Register read strobe.

31

32

33

34

35

36

37

IN10

IN11

IN12

IN13

IN20

IN21

IN22

SW5

SW6

SW7 Inputs to U5 indicating the switch

SW8 positions.

SW1

SW2

SW3

38 CLKO 40 kHz clock which drives the U5 clock input

(crystal frequency divided by 80).

39

40

XTALI

XTALO

Connections to the crystal oscillator.

Loading...

Loading...