Theory of Operation: Controller 3-35

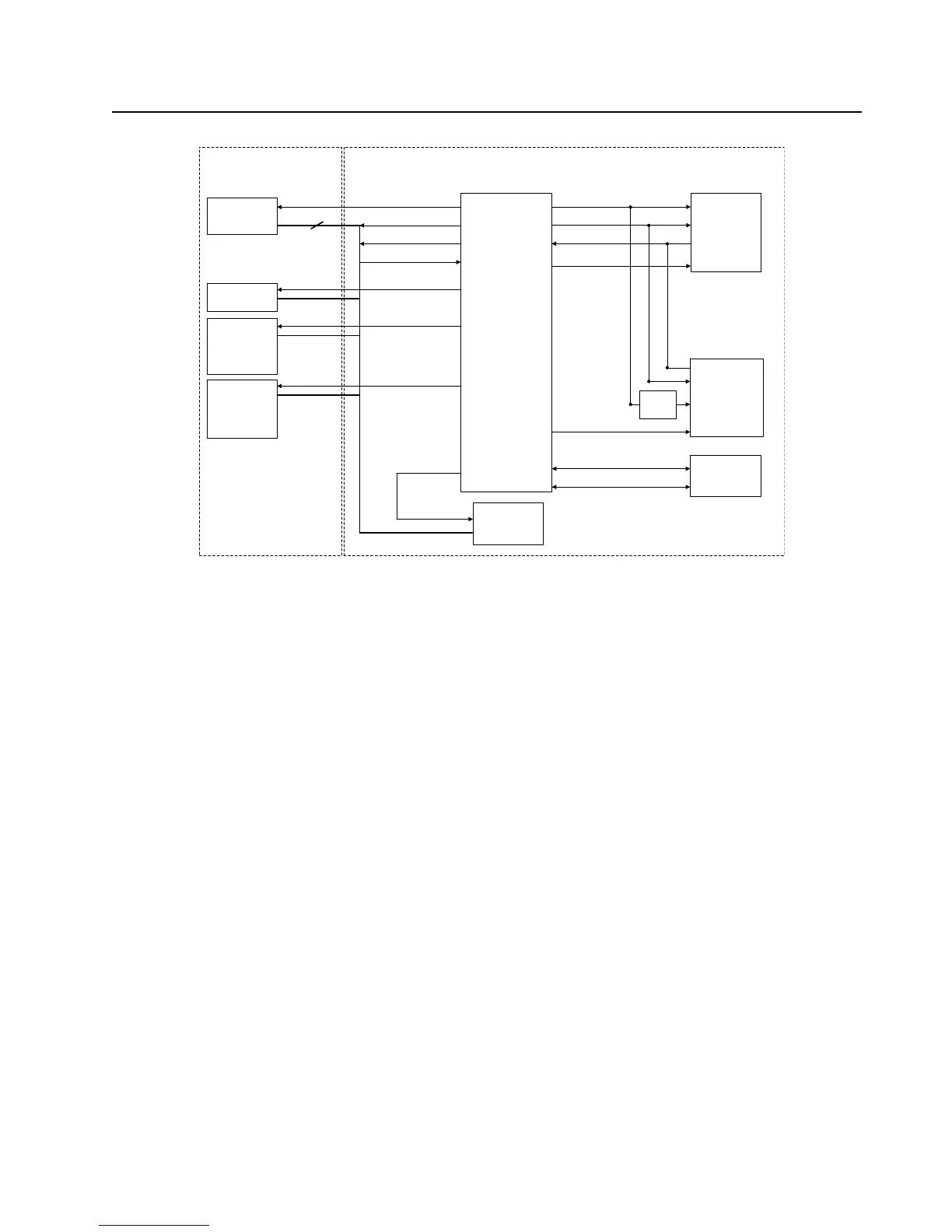

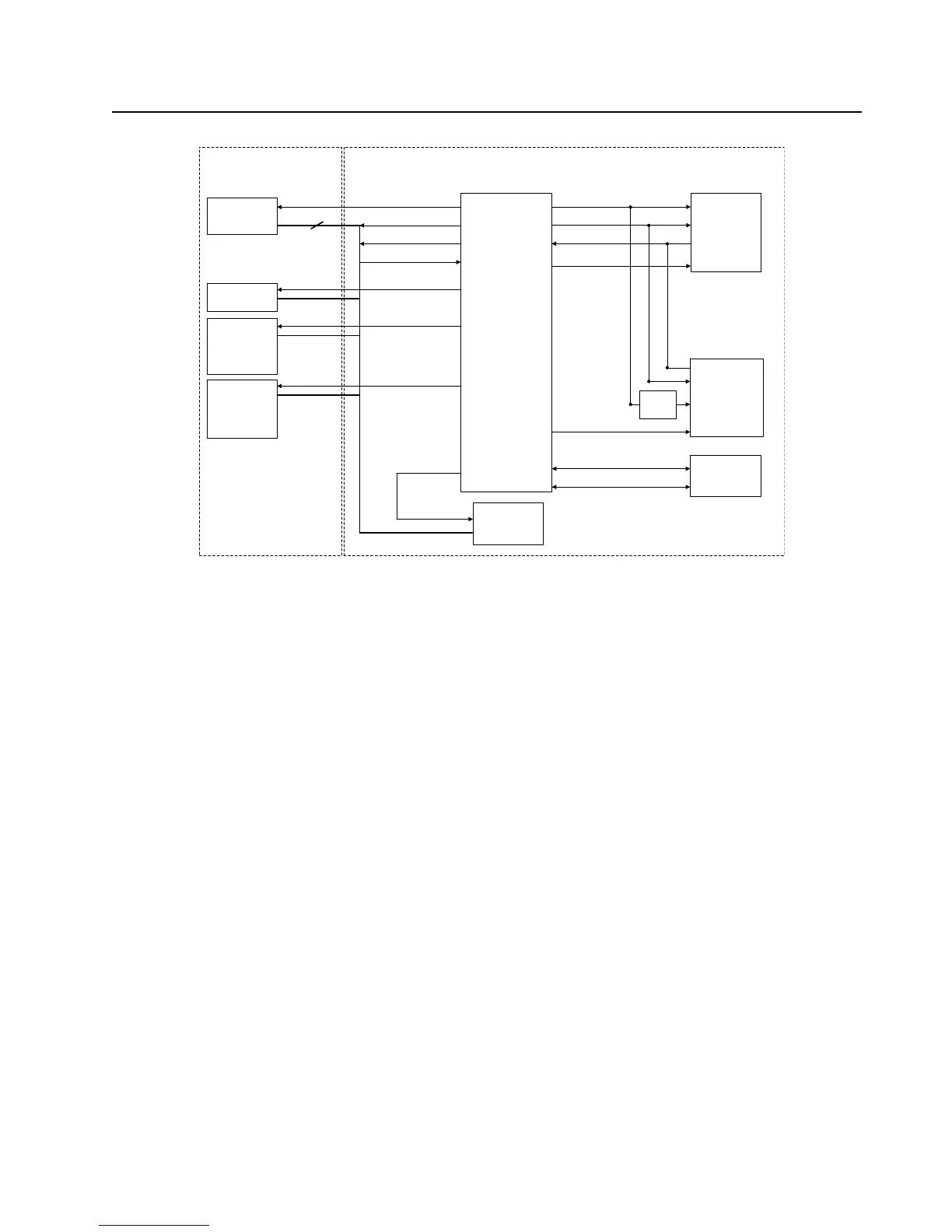

Figure 3-24. SPI and I2C Configuration

3.2.4.8.5 1-Wire

The OMAP's 1-wire line is available on the Main Board Connector J2302 pin 19. The signal is routed

through the keypad flex, keypad, front kit flex and GCAI flex.

3.2.4.8.6 USB

The OMAP CPU's USB port is routed to the side connector via J2302. The USB signals on the side

connector are illustrated in Figure 3-20.

3.2.4.8.7 UARTs

Two of OMAP's UARTs are configured for peripheral interfacing.

The four-wire UART1, which is capable of hardware flow control, is available on the side connector

for accessory devices. The signals are level translated via MAKO and routed to the side connector

via J2302.

OMAP's UART2, which is a two wire interface, capable of software flow control only, is connected to

the GPS receiver IC on the Main board.

3.2.4.8.8 CPLD (U6101)

The CoolRunner IC is a complex programmable logic device (CPLD) programmed specifically for the

APX product line. The CoolRunner IC is flash based and comes pre-programmed. It is contained in

an 8x8mm, 132 BGA package with 0.5mm ball spacing. The primary functions of the CPLD are clock

generation, GPIO expansion, SSI clock and frame sync direction control, F2 multiplexing, secure

data control, main display off-loading, and clock inversion.

An external linear regulator, U6508, supplies the CPLD's 1.875 V core voltage. The 1.875 V core

voltage is used for the CPLD’s internal logic and I/O buffers. MAKO's 24.576 MHz clock source is

used by the CPLD to generate a 32.768 kHz clock for OMAP booting, real time clock/timer, and for

GPS.

OMAP 1710

McBSP3 SPIF

DSP SPI

FRONT DISPLAY

MAKO

TI CODEC

ARM SPI

I2C

LIGHTING

CONTROLLERS

3

SPI_CLK

SPI_MOSI

SPI_MISO

MAKO_CS

CPLD

Inverter

I2C_SCL

I2C_SDA

COLOR_DIS_CS

SPI_DSP_CLK

SPI_DSP_MOSI

SPI_DSP_MISO

DAC_CS

EEPROM_CS

ABACUS_CS

ABACUS_CS

DSP SPI

TRIDENT

ABACUS

EEPROM

DAC

RF SECTION

CONTROLLER SECTION

CODEC_CS

I2C

Loading...

Loading...