Note*:

This memory is incorporated into the ASIC (IC501) and used for the image processing.

Fig. A shows the memory map of the Image Data RAM.

7.3.4. FLASH MEMORY (IC523)

The 512KB ROM (FLASH MEMORY) carries a common area of 32KB and bank areas which each

have 8KB (BK4~BK63). The addresses from 0000H to 7FFFH are for the common area and from

8000H to 9FFFH are for the bank areas.

7.3.5. DYNAMIC RAM (IC503)

The DRAM serves as CPU and receives memory.

The address is F200H~F3FFH (DRAM access window 1) and F600H~F7FFH (DRAM access

window 2).

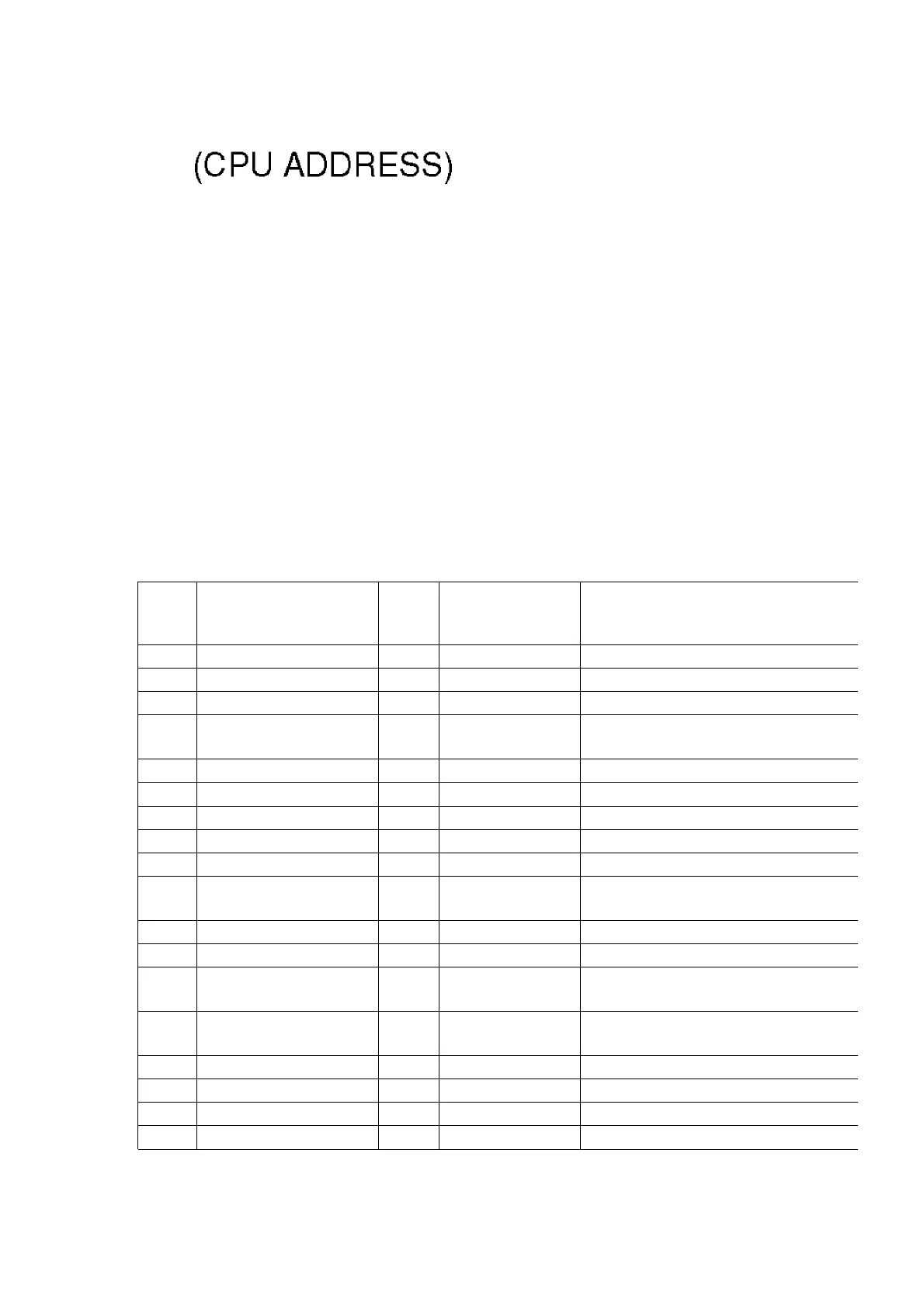

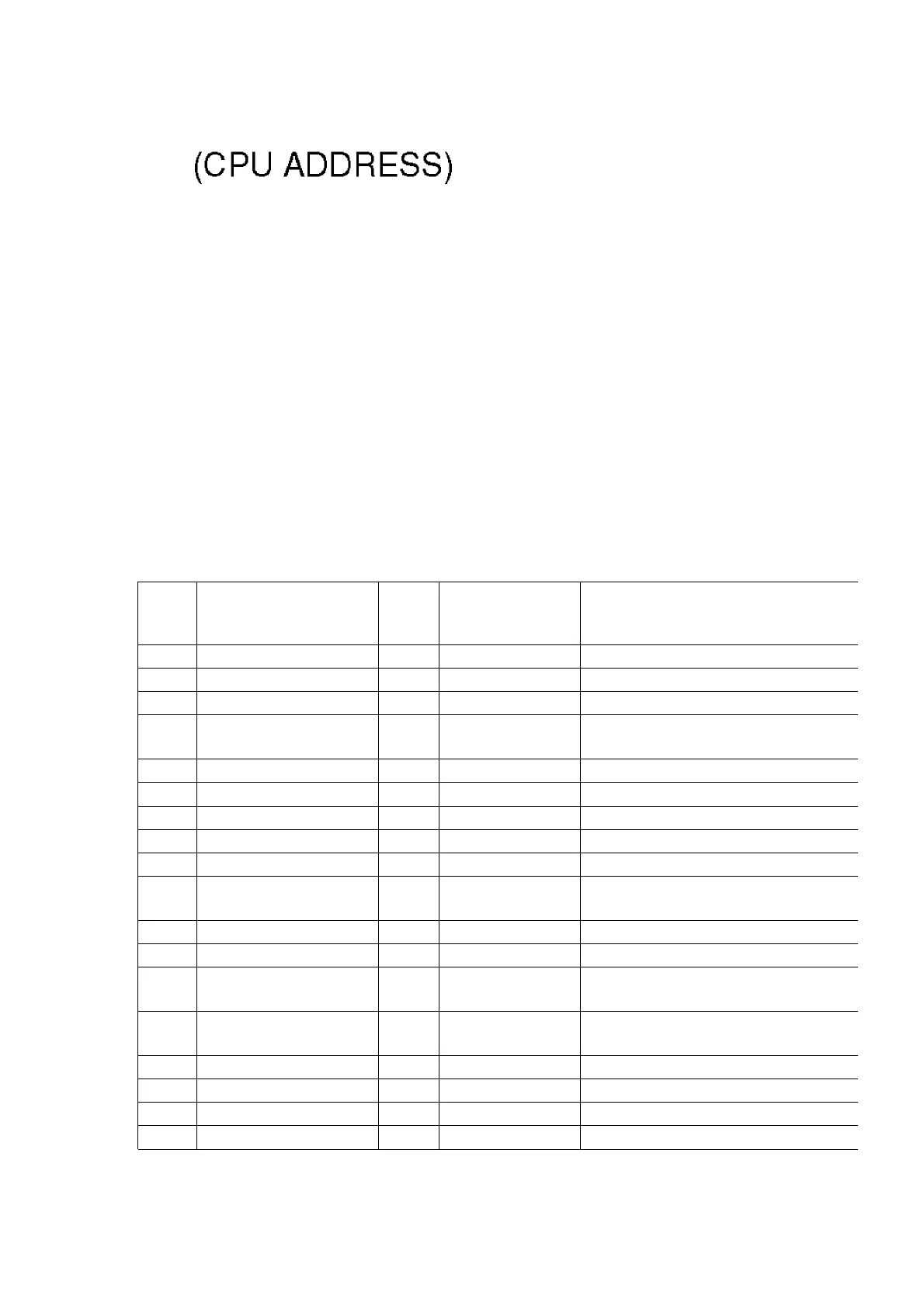

Descriptions of Pin Distribution (IC501)

NO. SIGNAL I/O POWER

SUPPLIED

VOLTAGE

DESCRIPTION

1 VSSA GND POWER SOURCE (ANALOG GND)

2 VDDA 3.3 3.3V POWER SOURCE (ANALOG +3.3V)

3 AIN1 A 3.3V CCD IMAGE SIGNAL INPUT

4 AIN2 A 3.3V THERMISTOR TEMPERATURE

INPUT

5 AIN3 A 3.3V -----------

6 AMON A 3.3V ANALOG SIGNAL MONITOR

7 VSS GND POWER SOURCE (GND)

8 X32OUT O 3.3V/BATT RTC (32.768KHz) CONNECTION

9 X32IN I 3.3V/BATT RTC (32.768KHz) CONNECTION

10 VDD (3.3V / B) ----- POWER SOURCE (+3.3V/LITHIUM

BATTERY)

11 XBACEN I 3.3V/BATT BACKUP ENABLE

12 XRAMCS O 3.3V/BATT NOT USED

13 VDD (3.3V / B) ----- POWER SOURCE(+3.3V / LITHIUM

BATTERY)

14 VDD (2.5V/B) ----- POWER SOURCE (+2.5V / LITHIUM

BATTERY)

15 FTG O 3.3V SH SIGNAL OUTPUT FOR CIS (SI)

16 F1 O 3.3V 01 SIGNAL OUTPUT FOR CIS (CLK)

17 F2/OP O 3.3V OUTPUT PORT (HSTXMUTE)

18 FR/OP O 3.3V OUTPUT PORT (MDMRST)

153

Loading...

Loading...