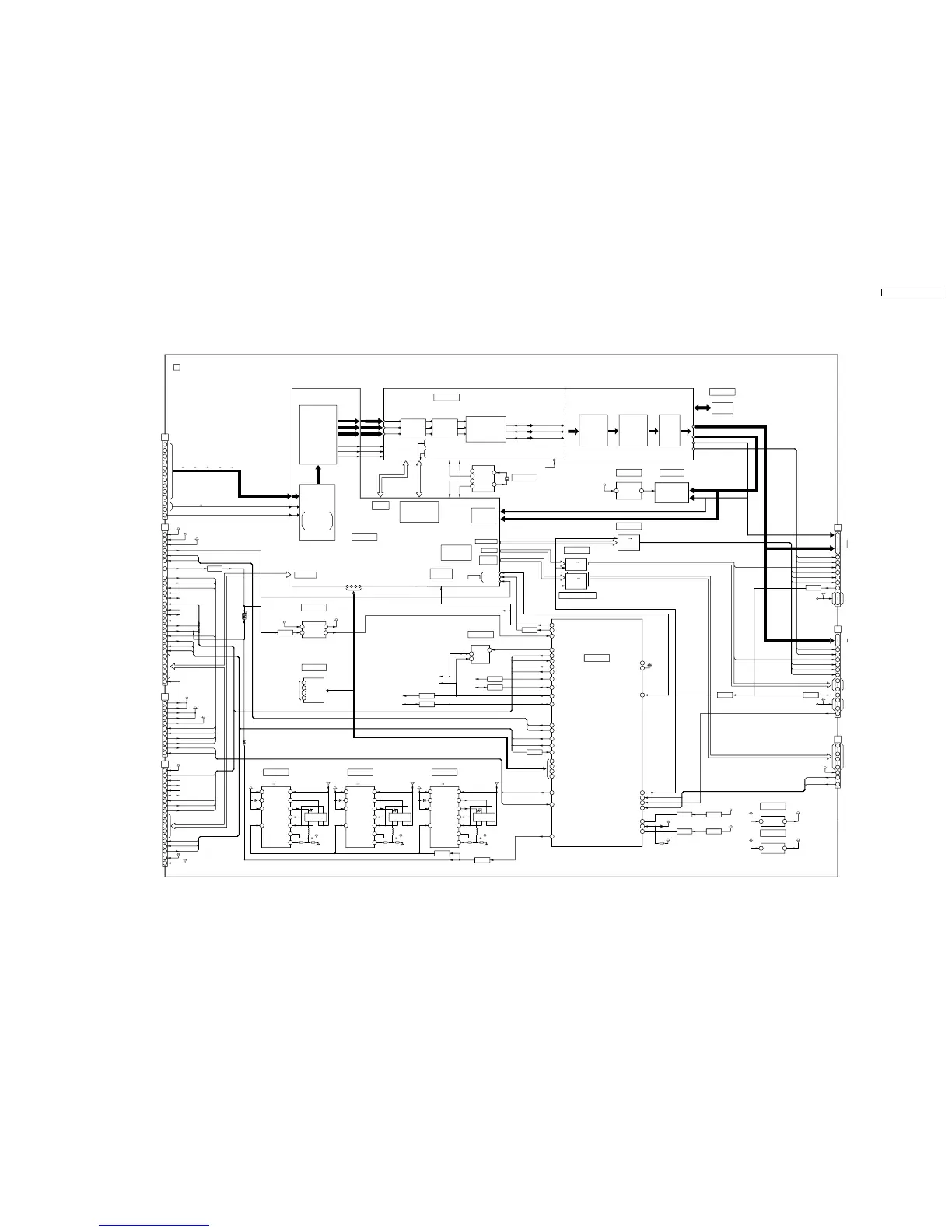

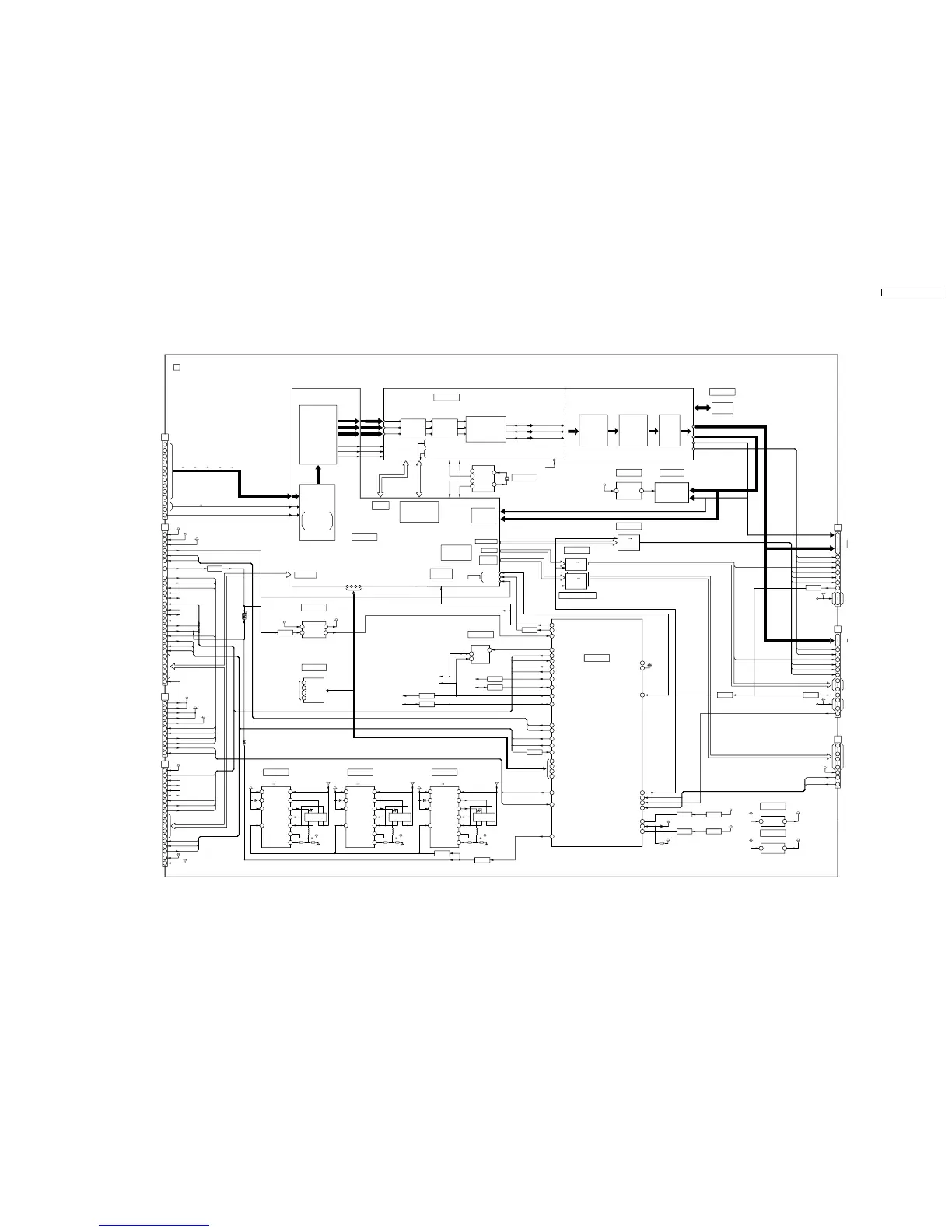

14.35. D-Board Block Diagram

CLKD0

CLKD1

TXD_PC

RXD_PC

PANEL_MAIN_ON

ALARM

READY

ECO_ON

TUNER_SUB_ON

TUNER_SUB_ON

CLKM_IN

FREE_RUN

DRVMUTE

RXD_PC

IIC_INT

TXD_PC

RXD_PC

IIC_CONT

IIC_INT

STB_SDA01

STB_SCL01

SOS8_SS

CLKD3

READY

ALARM

LED_R

REMOCON

IIC_CONT

TXD_PC

SOS6_SC1

SOS7_SC2

SOS7_SC2

SOS6_SC1

CLKD2

SOS4_PS

REMOCON

LED_R

LED_G

LED_R

LED_G

REMOCON

LED_G

SOS4-PS

STB_SCL02

STB_SDA02

CLRD

PCD1

LED

PCD2

CLRD

LED

ALL_OFF

AC_GOOD

IIC_INT

ALL_OFF

ECO_ON

AC_GOOD

PANEL_MAIN_ON

IIC_CONT

X9200

TP9372

TP9304

R 10bit

Scan Control DATA 13bit

IIC/INT

G 10bit

B 10bit

(D)PDB1

(D)PBUSY

B 10bit

(D)PDB0

R 10bit

(D)PSTB

(D)PSLCT

Sustain Control DATA 6bit

G 10bit

IC9503

4

10

PROCESSOR

DRIVER

TO C11

TO C21

14

50

13

51

26

15

TXD1

27

RXD1

IIC_CONT

IIC_INT

LVDS INPUT

DISCHARGE

CONTROL

IIC1_SDA

28

LEVEL CONVERTER

IIC2_SCL

29

12

15

Voltage

10

IIC2_SDA

14

21

IC9500

22

FPGA,ASIC

55

LSI_RST

XRST

SUB-FIELD

PLASMA AI/SUB FIELD PROCESSOR/DATA DRIVER

IC9003

IC9303

MICOM

XIN

XOUT

X9000

44

9.216MHz

IC9802,03

42

17

19

5

IIC1_SCL

Video DATA 48bit(DA0-DC14)

3.3V 5V

Low

3.3V 5V

ROMDATA04-15(ROMADDRESS00-20)

D32

D31

5VDET

46

1

TO DA2

D3

SOS7_SC2

76

73

72

SOS8_SS

5

READY

ALARM

67

DRVMUTE

IC9011

IIC_DATA1

IIC_CLK1

22

TUNER_SUB_ON

35

ALARM

33

34

DISPEN

37

READY

PANEL_STBY_ON

27

30

21

ECO_ON

4

2

RXD

TXD

6

D5

E+LVDSCLK

(RX_TCLK+)

E-LVDS2

(RX_TC-)

14

TO DA5

E-LVDS3

(RX_TD-)

16

7

15

11

12

E-LVDS1

(RX_TB-)

10

4

E-LVDS4

(RX_TE-)

1

9

E-LVDS0

(RX_TA-)

2

E-LVDSCLK

(RX_TCLK-)

E+LVDS2

(RX_TC+)

E+LVDS1

(RX_TB+)

E+LVDS4

(RX_TE+)

5

E+LVDS3

(RX_TD+)

LVDS_DET

STBY5V

+5V

D25

9

PANEL_MAIN_ON

ECO_ON

1

+5V

7

2

13

+15V

15

+15V

17

10

TO P25

F_STBY_ON

RXD

13

14

8

6

TXD

7

SDA1

PDB0

4

PSTB

5

IIC_INT

11

PSLCT

PBUSY

9

D6

SCL1

12

15

LED_R

PDB1

17

16

LED_G

st-r

IC9900

CONVERTER

XRST

CTI/TINT

WB-ADJ

I/P

COLOR

FORMAT CONVERTER/RGB PROCESSOR

CONVERTER

CONTRAST

FORMAT

Differential

Signaling

RECEIVER

FPGA

SOS4-PS

74

PANEL_MAIN_ON

24

P_ON/OFF

Q9057

Q9058

Q9055

Q9056

P3V_SCL02

P3V_SDA02

TO SC20

D20

2

9

13

20

SCAN

DATA

11

12

1

DRV_SOS7

P5V

DRV_SOS2

21

43

14

12

5VDET

53

55

20

SOS6_SC1

SUSTAIN

DATA

51

46

1

3

SS_SOS8

P3V_SCL1

P3V_SDA1

P15V

P5V

STB5V_M

NRST

DRV_RST

DATA DRIVER

16M FLASH MEMORY

RESET

45

VOUTVCC

IC9502

RESET

P3.3V

SS PULSE

SCAN OUT

SC PULSE

3.3V 5V

IC9504

37

UMH,UML,USH,USL,UEH,NUEL,ODED1,ODED2

CL,CLK,SIU,SID,SCSU,CEL2,CPH,CEL,CBK,CSL,CSH,CML,CMH

IC9901

DDR SDRAM(128M)

Q9302

Q9301

CLK4

17

CLK8

CLK1

21

24

7

CLK7

X1

1

28

X2

IC9200

PCK OCK

D

P3V_SCL1

P3V_SDA1

P5V

CONTROL

STBY5V

P15V

21

19

NCS

ASDIO

DATA 0

DCLK

ODED1

P5V

Control DATA

70

SOS3_3V

SOS2_15V

69

71

SOS5_5V

Q9054 Q9053

Q9052 Q9051

P5V

P15V

3.3V

STB 5V_M

STBY 5V 29

LEVEL CONVERTER

LEVEL CONVERTER

CLOCK GENE.

DIGITAL SIGNAL PROCESSOR

PLASMA AI

SUB-FIELD PROCESSOR

FOR

FACTORY

USE

P5V

P5V

DRVCLKD0-D3

20bit

(DA8-DC14)

(DA0-DC7)

24bit

CLRD,LED,PCD1,PCD2

AVR P1.5V

VOUT

P2.5V

P1.5V

IC9801

61

VDD

(LSI58 COMM)

TDO,TDI

TMS,TCK

JTAGDCK

HD

VD

JTAG

PD1-MS

FPCLK

FPDAT0

FPDAT1

SFVRST

LATCH

SFRST

R0-R9

G0-G9

VD

B0-B9

HD

DCK

PICTURE

OUTPUT

LVDS

LVDS

SYNC PROCESSING

WB ADJ

DISCHARGE CONTROL

FLASH CONTROL

FPGA CONTROL

CONTROL

RESET

CONTROL

FLASH

CLKM PRCKI

-IN

STB 3.3V

20

Q9044

IIC_CLK2

16

17

IIC_DATA2

IC9001

6

5

EEPROM

SDA

SCL

1

WP

25

EEP_WR_CTL

P15V

STB5V_M

REMOCON

18

15V 2.5V

OUT2

G2

17

S1

19

D1

OUT1

21

D2

20

13

D1D2

VO

23

5

16

LX

VCC VIN

VDD

18

G1

IC9809

S2

DC-DC CONVERTER

24

FB

-INC

9

CTL

CB

P15V

P2.5V

Q9805

Q9806

23

NCS

DATA

ADSI

DCLK

10

IIC_CONT

1

2

STBY3.3V

STB3.3V

SDA2

SCL2

3

1

(D)P15V

6

NCS

36

37

ASDIO

38

DATA 0

DCLK

39

8

LED_G

REMOCON

9

LED_R

10

1

VOUT

RESET

34

VDD

CE

6

STB5V_M

Q9046

STB3.3V

9

RESET

Q9050

XRST

SOS9_CONF

34

DRVRST

Q9300

ODED1

ODED2

PLASMA AI

NEW

DATA

ROMDATA00-03

DQ4-DQ15

A0-A19

DQ0-DQ3

ROMDATA00-03

ROMDATA04-15/ROMADDRESS00-20

3bit

SOS4_PS

16

XRST

65

LED_R

REM_IN

66

16

LED_G

Q9010

STBY 3.3V

RA_E

,RB_E ,RC_E ,RD_E ,RE_E

RCLK_E

E+LVDS0

(RX_TA+)

STB_SCL02

STB_SDA02

STB_SDA02

STB_SCL02

DPCLK1

TSET

TERMINAL

(SC_SOS6)

(SC_SOS7)

P3.3V

STB_SDA02

STB_SCL02

P3V_SCL1

P3V_SDA1

1

2

5

6

D9802

Q9801

AVR 5V

51

VDD

P15V

VOUT

IC9806

LDO_5V

LDO_5V

VIN

VDD

G2

18

17

S1

19

D1

-INC

9

D1

CTL

CB

D2

24

FB

P15V

P3.3V

VO

23

LDO_5V

5

20

16

Q9803

D2

21

OUT1

G1

13

IC9807

S2

DC-DC CONVERTER

15V

3.3V

LX

VCC

OUT2

VO

23

LDO_5V

5

20

16

Q9800

D2

21

OUT1

G1

13

IC9800

S2

DC-DC CONVERTER

15V

1.2V

LX

VCC

OUT2

VIN

VDD

G2

18

17

S1

19

D1

-INC

9

D1

CTL

CB

D2

24

FB

P15V

P1.2V

DOUTDC15

DOUTDA8

CLK2

CLRD

CLK3

ODED1

LED

PCD1

(DA15-DC15)

,

13

15

P5V

CLK0

CLK1

DOUTDA0

DOUTDC7

35

5

38

CLRD

39

LED

PCD2

40

ODED2

(DA15-DC15)

ODED2

ALL OFF

23

18

ALL OFF

FORMAT CONVERTER

STB 3.3V

RESET

P+3.3V SOS / LED BLINKING : 3TIMES

P+5V SOS / LED BLINKING : 5TIMES

P+15V SOS / LED BLINKING : 2TIMES

25P5V

P5V

11AC_GOOD

DC_DC_ON

D9811

19

AC_GOOD

PROM(FPGA)

IC9007

IIC_CONT

19

TH-37/42PG9W

D-Board Block Diagram

TH-37/42PG9W

D-Board Block Diagram

TH-37PG9W / TH-42PG9W

105

Loading...

Loading...