5G Module Series

RM500Q-GL Hardware Design

RM500Q-GL_Hardware_Design 46 / 85

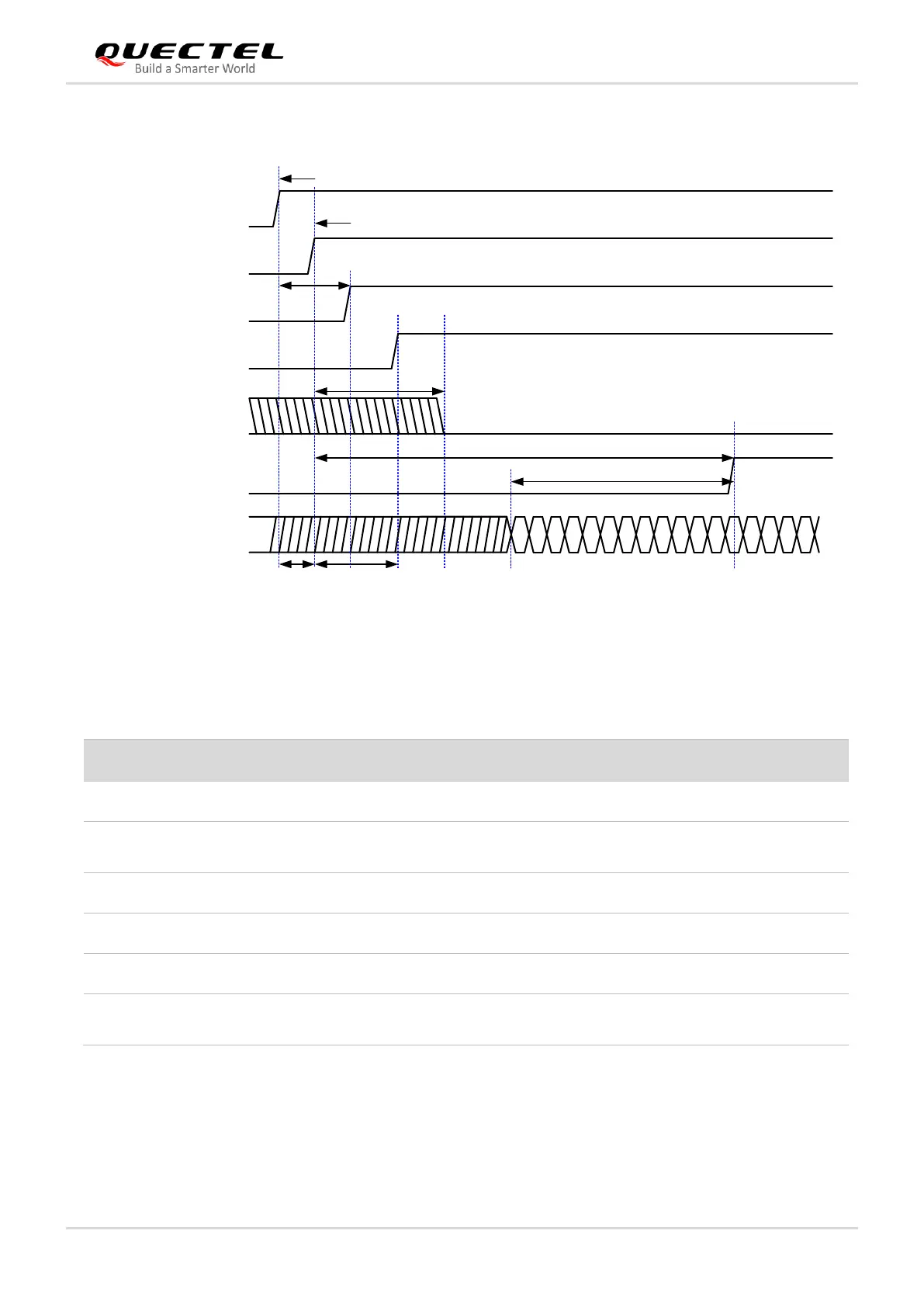

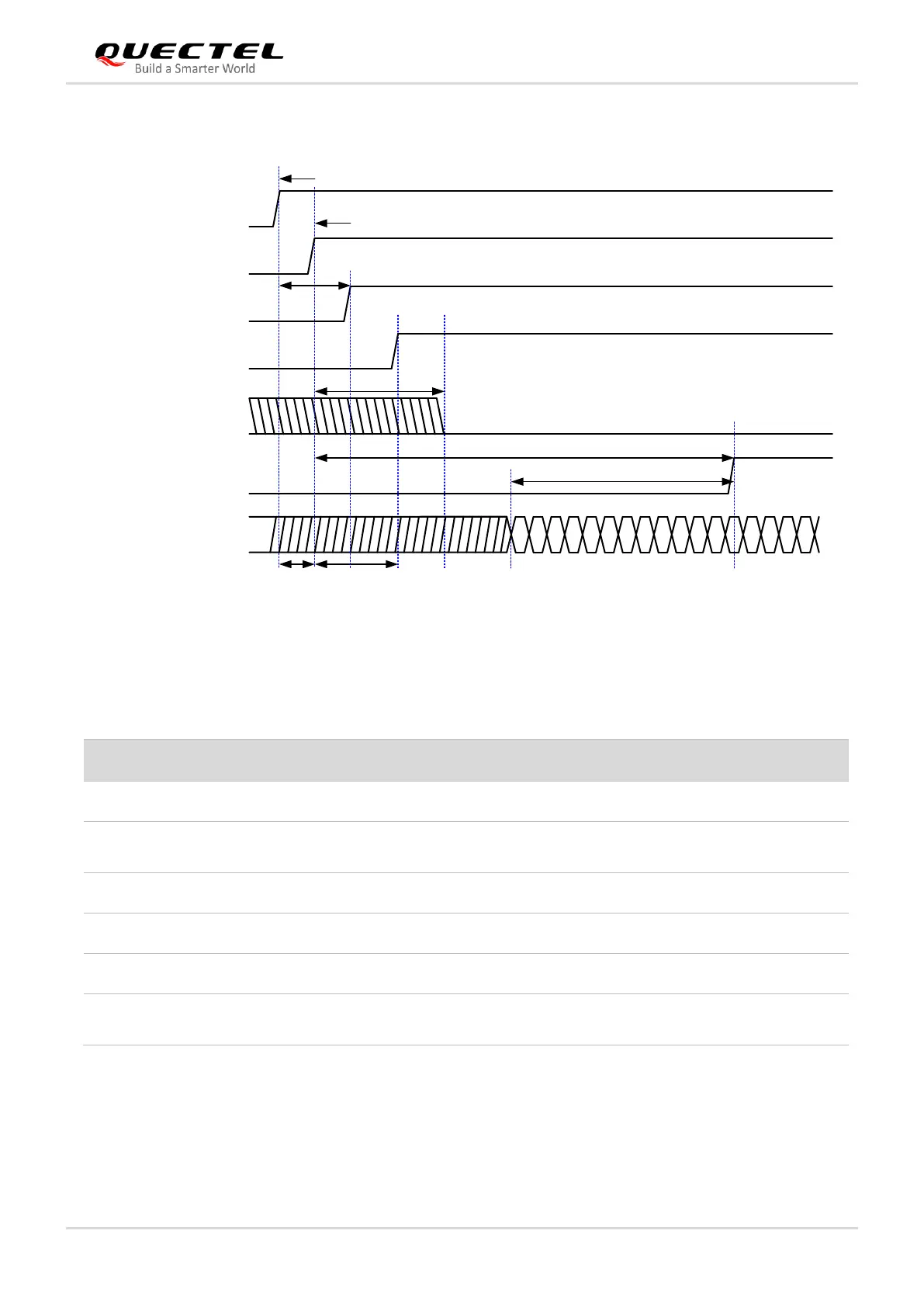

The following figure and table are PCIe turn-on timing and variables of the module.

T

FCPO#-CLKREQ#

> 90 ms

PCIE_CLKREQ_N

PCIE_RST_N

PCIE_REFCLK

T

power-on

T

turn-on

VCC

FCPO#

Module power-on or insertion detection

RESET#

RFFE_VIO_1V8

System turn-on and booting

V

IH

≥ 1.19 V

1.8 V

3.7 V

1.8 V

T

FCPO#-PERST#

> 100 ms

T

PERST#-CLK

> 100 us

T

VCC-RST#

Figure 21: PCIe Power-on Timing of the Module

Table 18: PCIe Turn-on Timing of the Module

Module power-on time depending on the host.

Time period between module power-on and

RESET# being driven HIGH.

Module system turn on time.

The time period during which REFCLK is stable

before PERST# is inactive.

Loading...

Loading...