5G Module Series

RM500Q-GL Hardware Design

RM500Q-GL_Hardware_Design 17 / 85

2.3. Evaluation Board

To help you develop applications conveniently with RM500Q-GL, Quectel supplies an evaluation board

(PCIe Card EVB), a USB to RS-232 converter cable, a USB type-B cable, antennas and other peripherals

to control or test the module. For more details, see document [3].

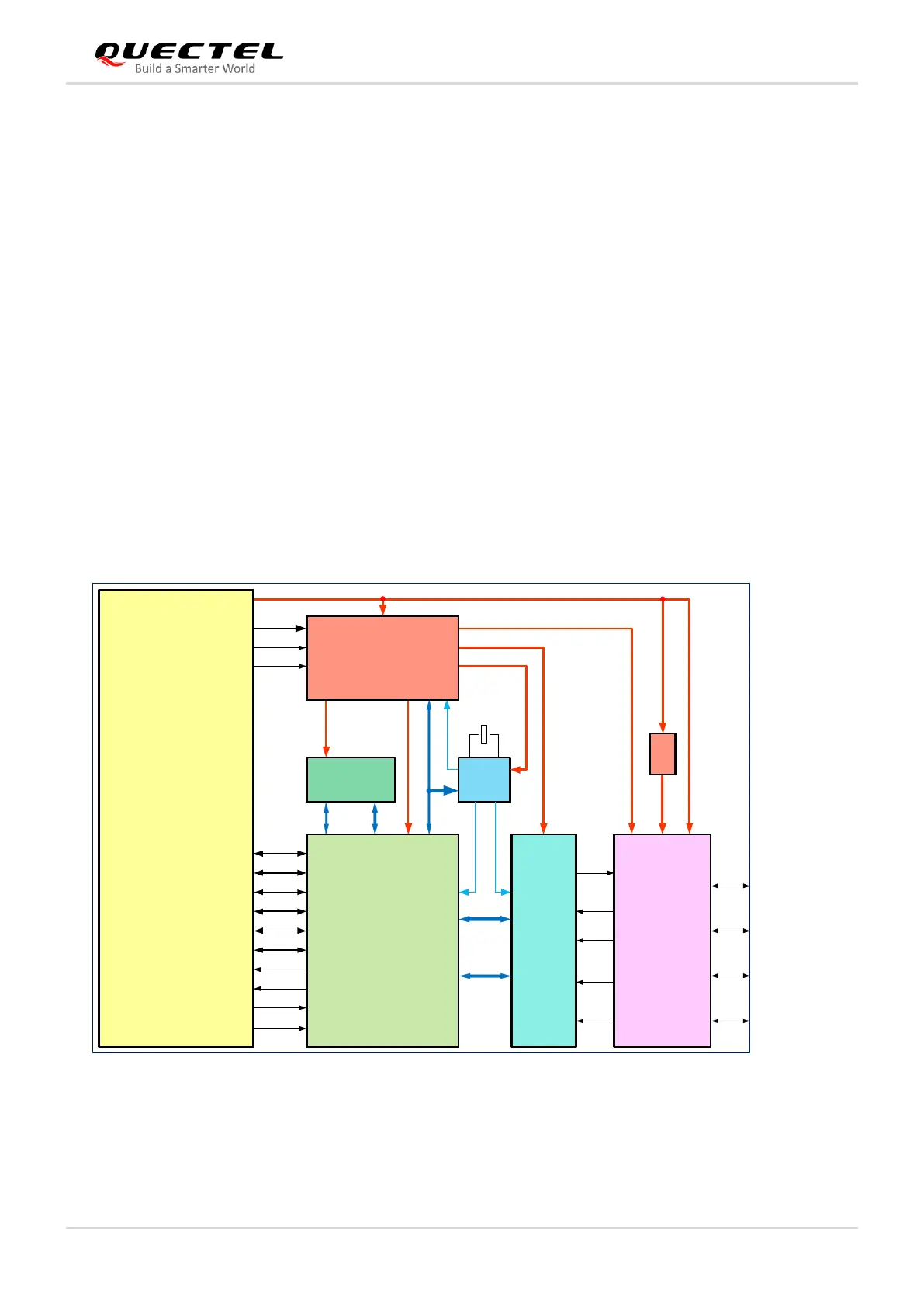

2.4. Functional Diagram

The following figure shows the functional diagram of RM500Q-GL.

⚫ Power management

⚫ Baseband

⚫ LPDDR4X SDRAM + NAND Flash

⚫ Radio frequency

⚫ M.2 Key-B interface

Loading...

Loading...