5G Module Series

RM500Q-GL Hardware Design

RM500Q-GL_Hardware_Design 33 / 85

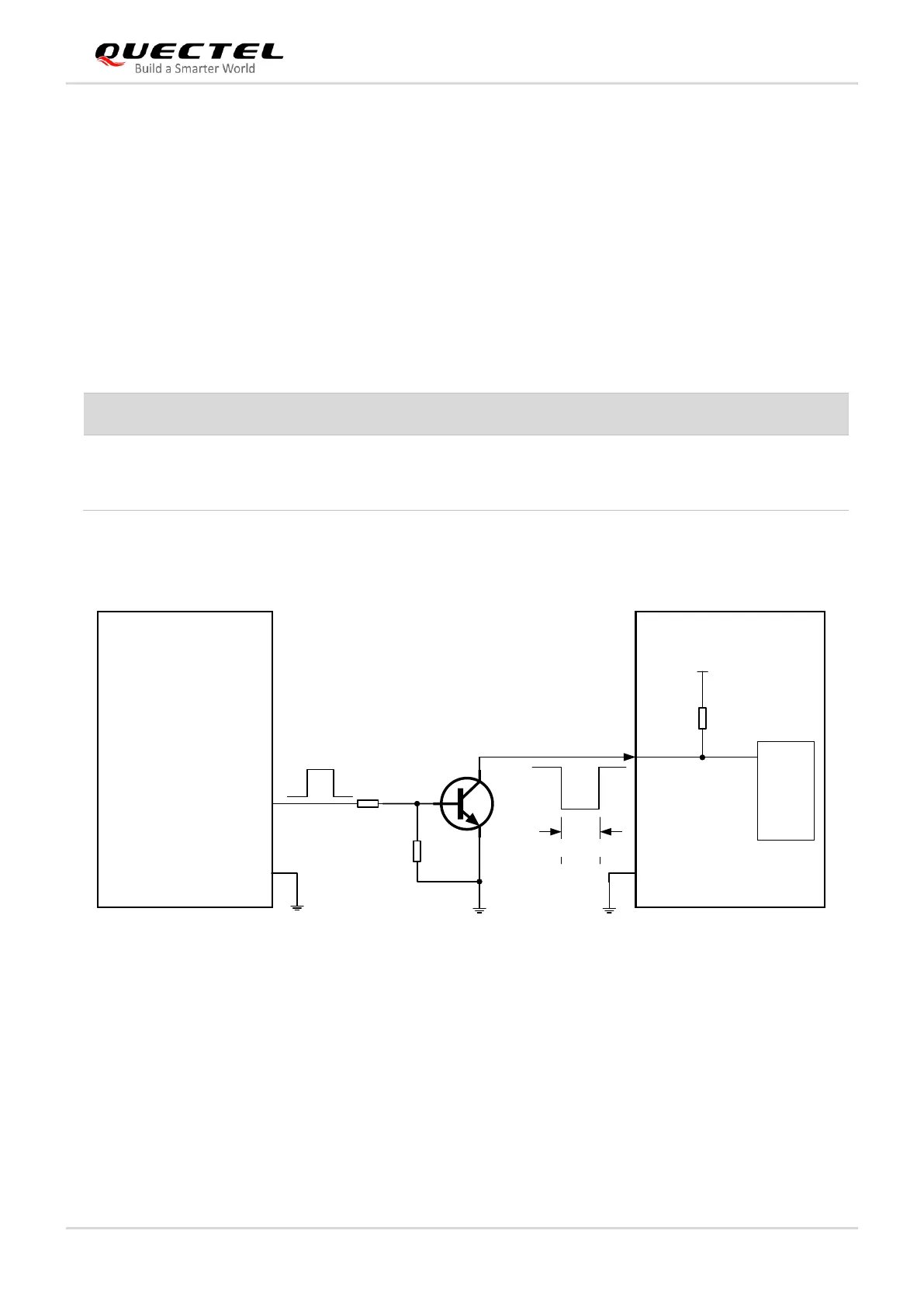

3.6. Reset the Module

RESET# is an asynchronous and active LOW signal (1.8 V logic level). Whenever this pin is active, the

module will immediately enter Power On Reset (POR) condition.

Please note that triggering the RESET# signal will lead to loss of all data in the modem and removal of

system drivers. It will also disconnect the modem from the network.

Table 12: Definition of RESET# Pin

The module can be reset by pulling down the RESET# pin for 200–980 ms. An open collector/drain driver

or button can be used to control the RESET# pin.

Loading...

Loading...