R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

Speed, byte 1

Bit 15 Bit 8

Register 17h: Speed, byte 0

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

Speed, byte 0

Bit 7 Bit 0

Bit 23-0 Speed, byte 2/1/0:

Speed of the motor feedback system (length: 24 bits)

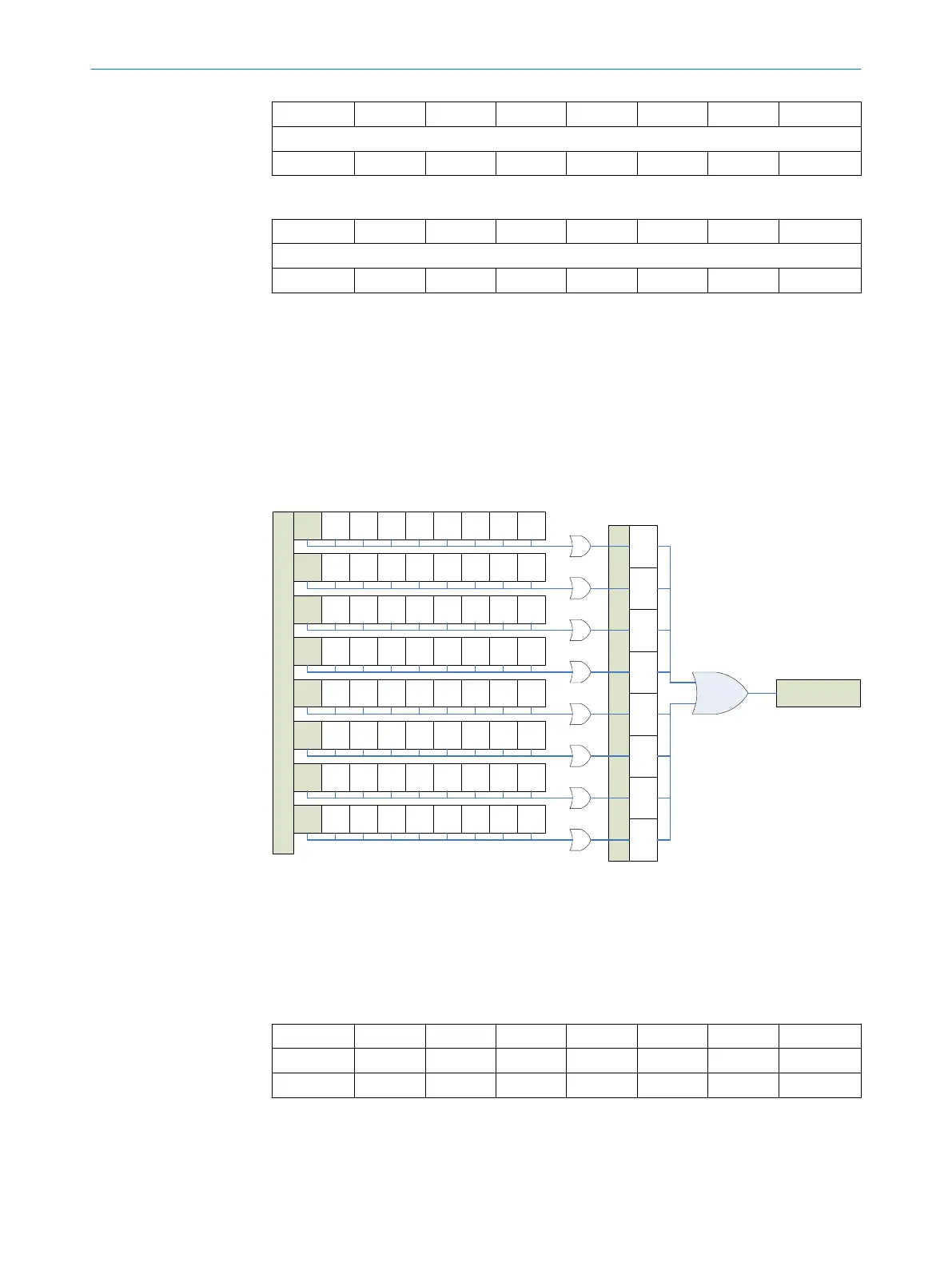

6.3.14 Status summary

The SUMMARY status summary register contains the summarized DSL Slave status

information. Each status summary bit contains the summarized information from 8

error, warning and event modes of the DSL Slave. The bits in the status summary regis‐

ter can be read only. figure 15 shows the relationship between the encoder status regis‐

ters, the status summary register and the SUM bit in the EVENT registers.

Encoder Status (DSL Slave registers)

Reg

40h

Bit

7

Bit SUM

(Reg 04h)

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Status Summary (Reg 18h DSL Master)

Reg

41h

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Reg

42h

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Reg

43h

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Reg

44h

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Reg

45h

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Reg

46h

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Reg

47h

Bit

7

Bit

6

Bit

5

Bit

4

Bit

3

Bit

3

Bit

1

Bit

0

Bit

0

Bit

1

Bit

2

Bit

3

Bit

4

Bit

5

Bit

6

Bit

7

Figure 15: DSL Slave status and summary

A bit that has been set in the SUMMARY register is not automatically deleted by the DSL

System. To delete, the frequency inverter application must read the corresponding DSL

Slave encoder status register (see chapter 6.4.1) and acknowledge the status message,

by individually deleting each set bit.

Register 18h: Status summary

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

SUM7 SUM6 SUM5 SUM4 SUM3 SUM2 SUM1 SUM0

Bit 7 Bit 0

Bit 7-1 SUM7:SUM1: Status summary bit (external resource)

1 = An error, a warning or an event associated with DSL Slave external resources was

triggered.

6

REGISTER MAP

46

T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Loading...

Loading...