STEP 5 Operations S5-115F Manual

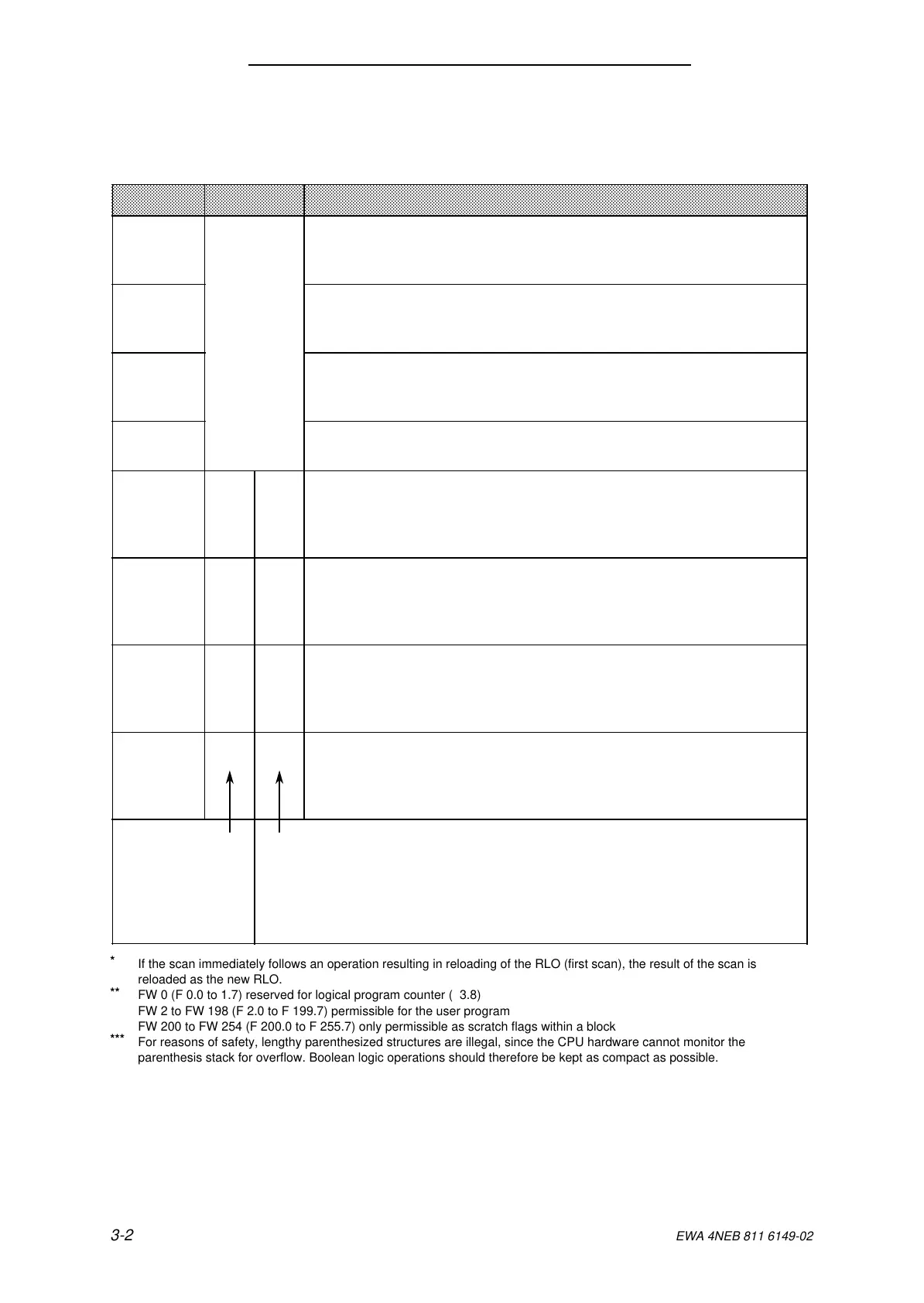

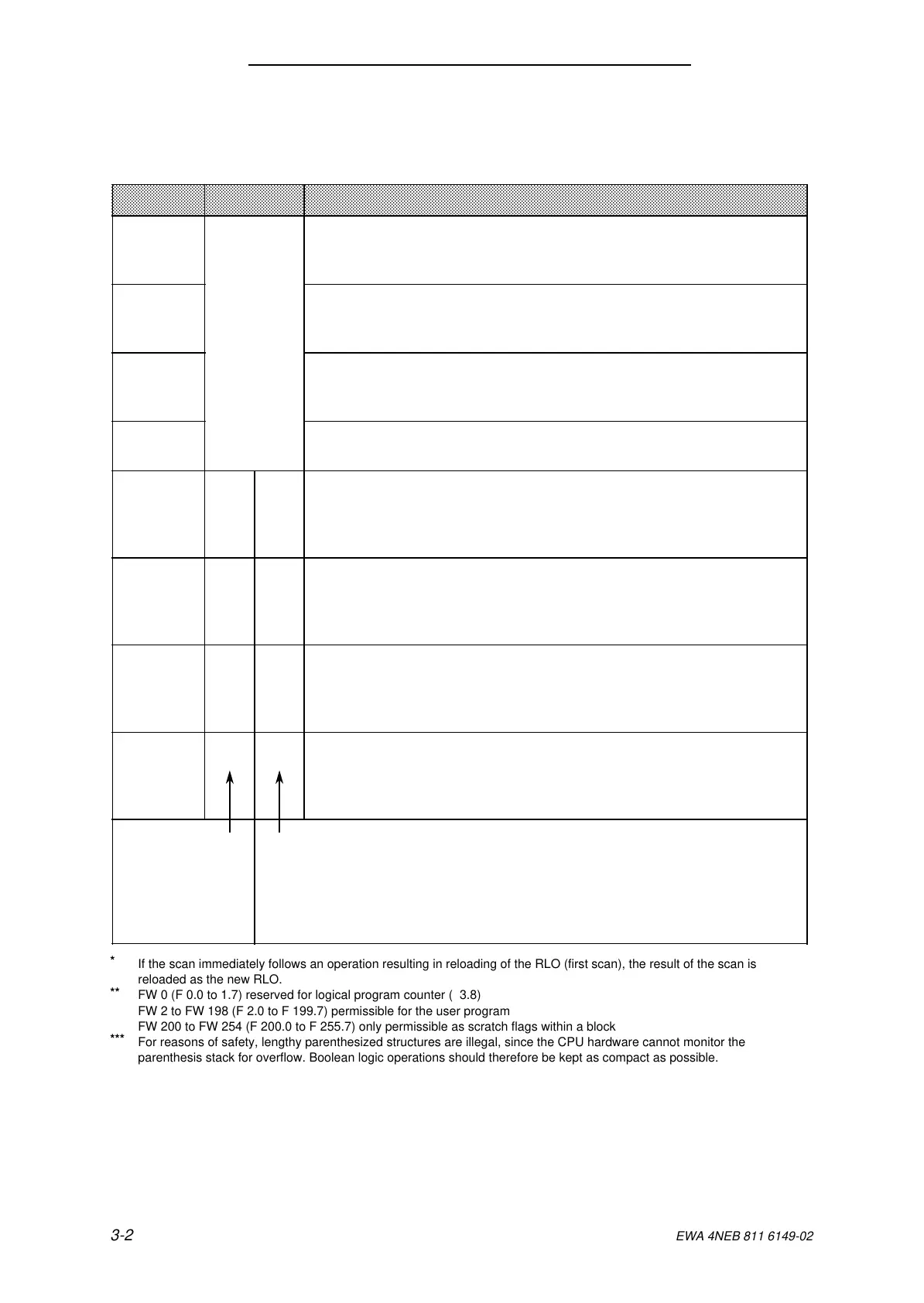

Table 3-1 provides an overview of Boolean logic operations. Examples follow the table.

Table 3-1. Overview of Boolean Logic Operations

Operation Meaning

Scan operand for ”1” and combine with RLO through logic AND.

The result is ”1” when the operand in question carries signal state

”1”. Otherwise the scan results in ”0”. Combine this result with the

RLO in the processor through logic AND.

*

Parameter CPU 942F

0.0 to 127.7

0.0 to 125.7

0.0 to 255.7

**

0 to 127

0 to 127

Operand

A

O Scan operand for ”1” and combine with RLO through logic OR.

The result is ”1” when the operand in question has signal state ”1”.

Otherwise the scan results in ”0”. Combine this result with the RLO

in the processor through logic OR.

*

Scan operand for ”0” and combine with RLO through logic AND.

The result is ”1” when the operand in question has signal state ”0”.

Otherwise the scan results in ”0”. Combine this result with the RLO

in the processor through logic AND.

*

Scan operand for ”0” and combine with RLO through logic OR.

The result is ”1” when the operand in question has signal state ”0”.

Otherwise the scan results in ”0”. Combine this result with the RLO

in the processor through logic OR.

*

ID

I

Q

F

T

C

AN

ON

O Combine AND operations through logic OR.

Combine the result of the next AND logic operation (RLO) with the

previous RLO through logic OR.

A(

***

Combine expression enclosed in parentheses through logic AND.

Combine the RLO of the expression enclosed in parentheses with

the previous RLO through logic AND.

O(

***

Combine expression enclosed in parentheses through logic OR.

Combine the RLO of the expression enclosed in parentheses with

the previous RLO through logic OR.

)

***

Right parentheses.

Conclude the expression enclosed in parentheses.

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

a

*

If the scan immediately follows an operation resulting in reloading of the RLO (first scan), the result of the scan is

reloaded as the new RLO.

**

FW 0 (F 0.0 to 1.7) reserved for logical program counter ( 3.8)

FW 2 to FW 198 (F 2.0 to F 199.7) permissible for the user program

FW 200 to FW 254 (F 200.0 to F 255.7) only permissible as scratch flags within a block

***

For reasons of safety, lengthy parenthesized structures are illegal, since the CPU hardware cannot monitor the

parenthesis stack for overflow. Boolean logic operations should therefore be kept as compact as possible.

3-2

EWA 4NEB 811 6149-02

Loading...

Loading...