FN990

Family Hardware Design Guide

1VV0301752 Rev. 3 Page 22 of 92 2022-10-07

Not Sub

ect to NDA

3. PINS ALLOCATION

Pin-out

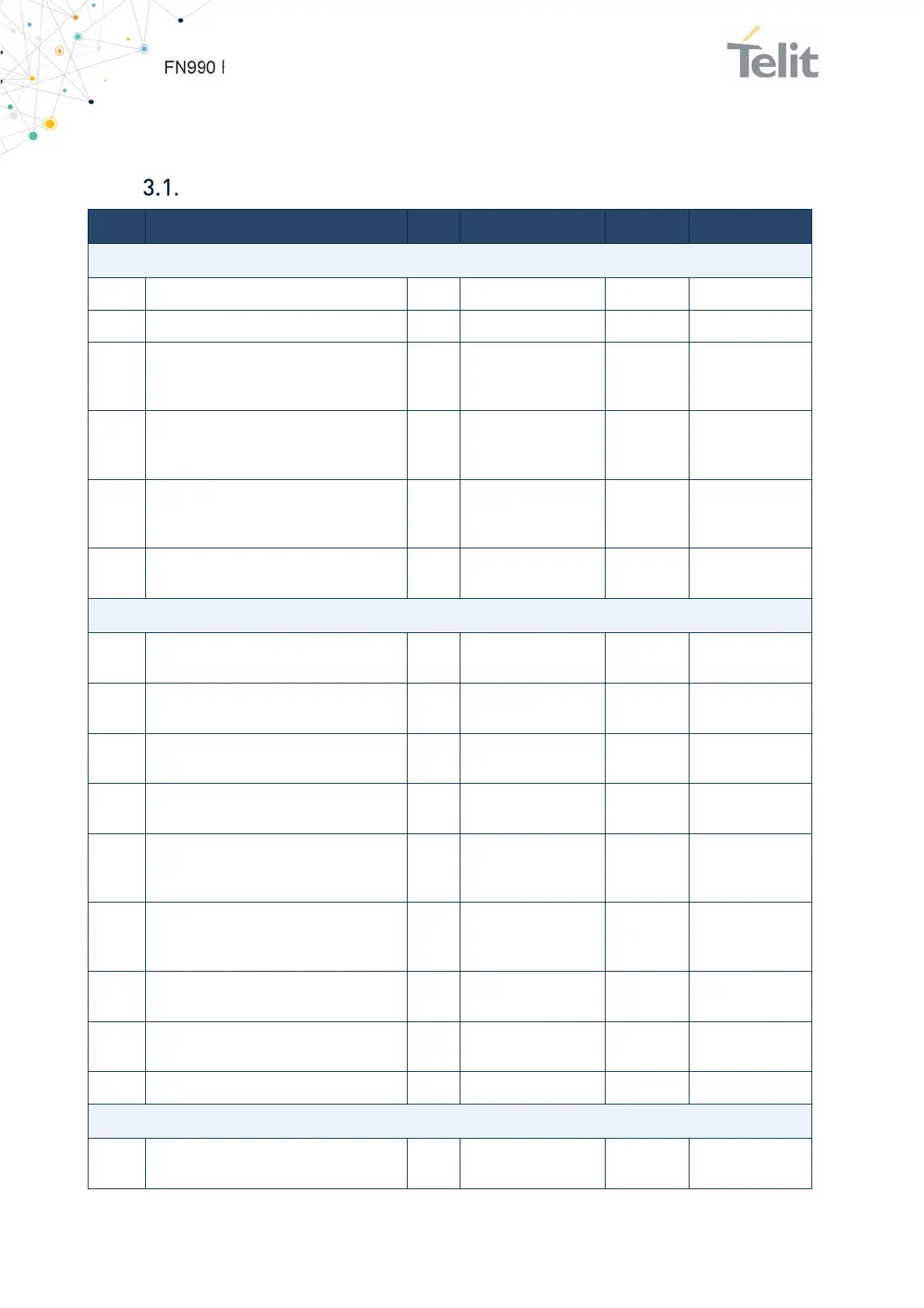

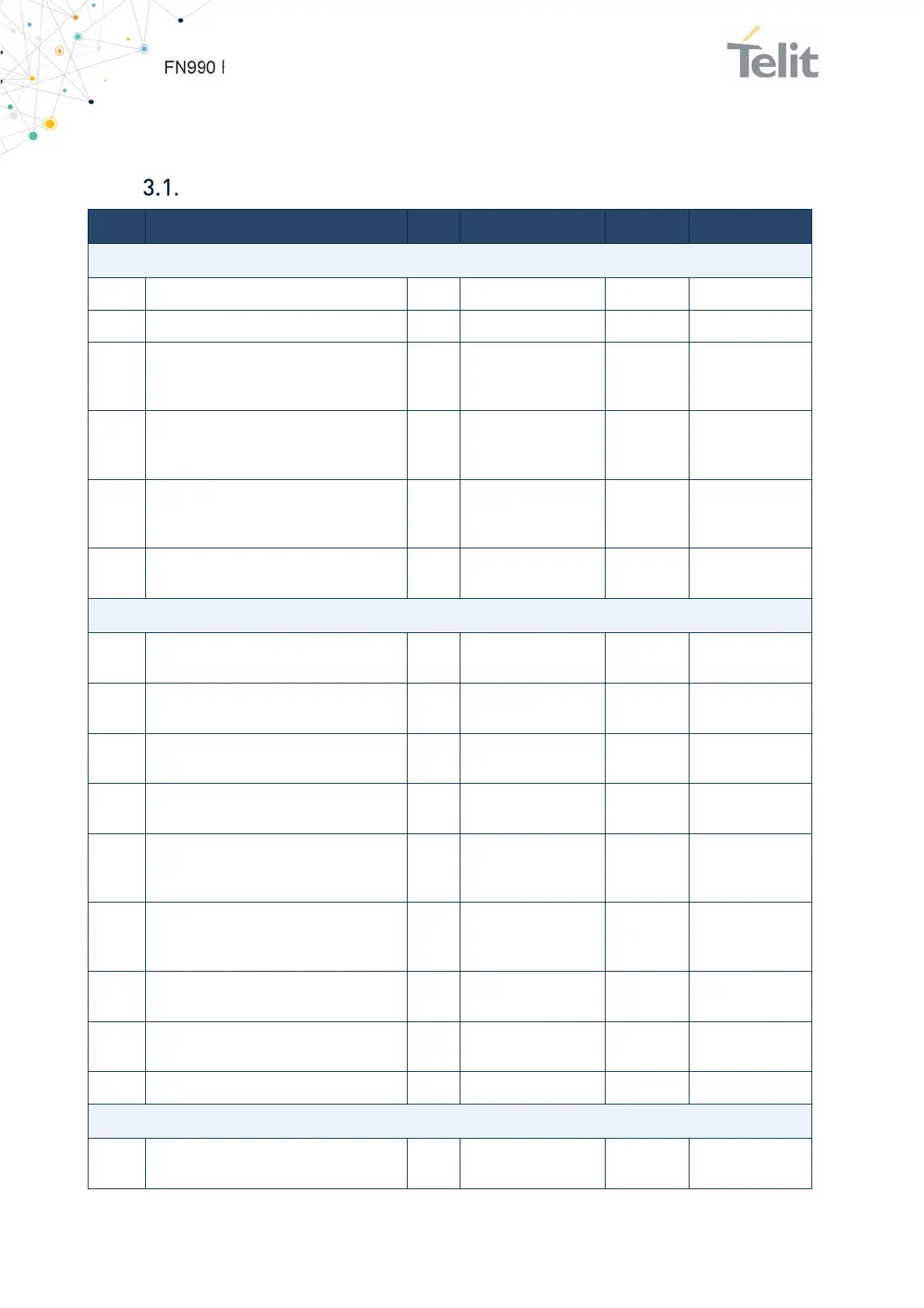

Pin Signal I/O Function Type Comment

USB Communication Port

7 USB_HS_DP I/O USB 2.0 Data Plus Analog

9 USB_HS_DM I/O USB 2.0 Data Minus Analog

29 USB_SS_TX_M O

USB 3.1 super-

speed transmit –

Minus

Analog

31 USB_SS_TX_P O

USB 3.1 super-

speed transmit –

Plus

Analog

35 USB_SS_RX_M I

USB 3.1 super-

speed receive –

Minus

Analog

37 USB_SS_RX_P I

USB 3.1 super-

speed receive – Plus

Analog

PCIe Communication Port

41 PCIE_TX0_M O

PCIe transmit 0 –

Minus

Analog

43 PCIE_TX0_P O

PCIe transmit 0 –

Plus

Analog

47 PCIE_RX0_M I

PCIe receive 0 –

Minus

Analog

49 PCIE_RX0_P I

PCIe receive 0 –

Plus

Analog

53 PCIE_REFCLK_M I

PCIe differential

reference clock –

Minus

Analog

55 PCIE_REFCLK_P I

PCIe differential

reference clock –

Plus

Analog

50 PCIE_RESET_N I

Functional reset to

PCIe bus

VPH_PWR Default PU

52 PCIE_CLKREQ_N O

PCIe reference

clock request signl

VPH_PWR Internal 100k PU

54 PCIE_WAKE_N O PCIe wake-up VPH_PWR Internal 100k PU

SIM Card Interface 1

36 UIM1_VCC

O

Supply output for an

external UIM1 card

1.8V /

2.95V

Power

Loading...

Loading...