• 16-bit down or up-down counter, with repeat-reload mode

• Selectable and configurable clock source

• 8-bit programmable prescaler to divide the counter clock frequency

• Repeat counter to generate an interrupt or event only after a given number of cycles of the counter

• Up to four independent channels for

– Output compare

– Input capture

– PWM output

– One-shot mode

• Shadow register for load and CC register available in both TIMA0 and TIMA1

• Complementary output PWM

• Asymmetric PWM with programmable dead band insertion

• Fault handling mechanism to ensure the output signals in a safe user-defined state when a fault condition is

encountered

• Support synchronization and cross trigger among different TIMx instances in the same power domain

• Support interrupt and DMA trigger generation and cross peripherals (such as ADC) trigger capability

• Two additional capture/compare channels for internal events

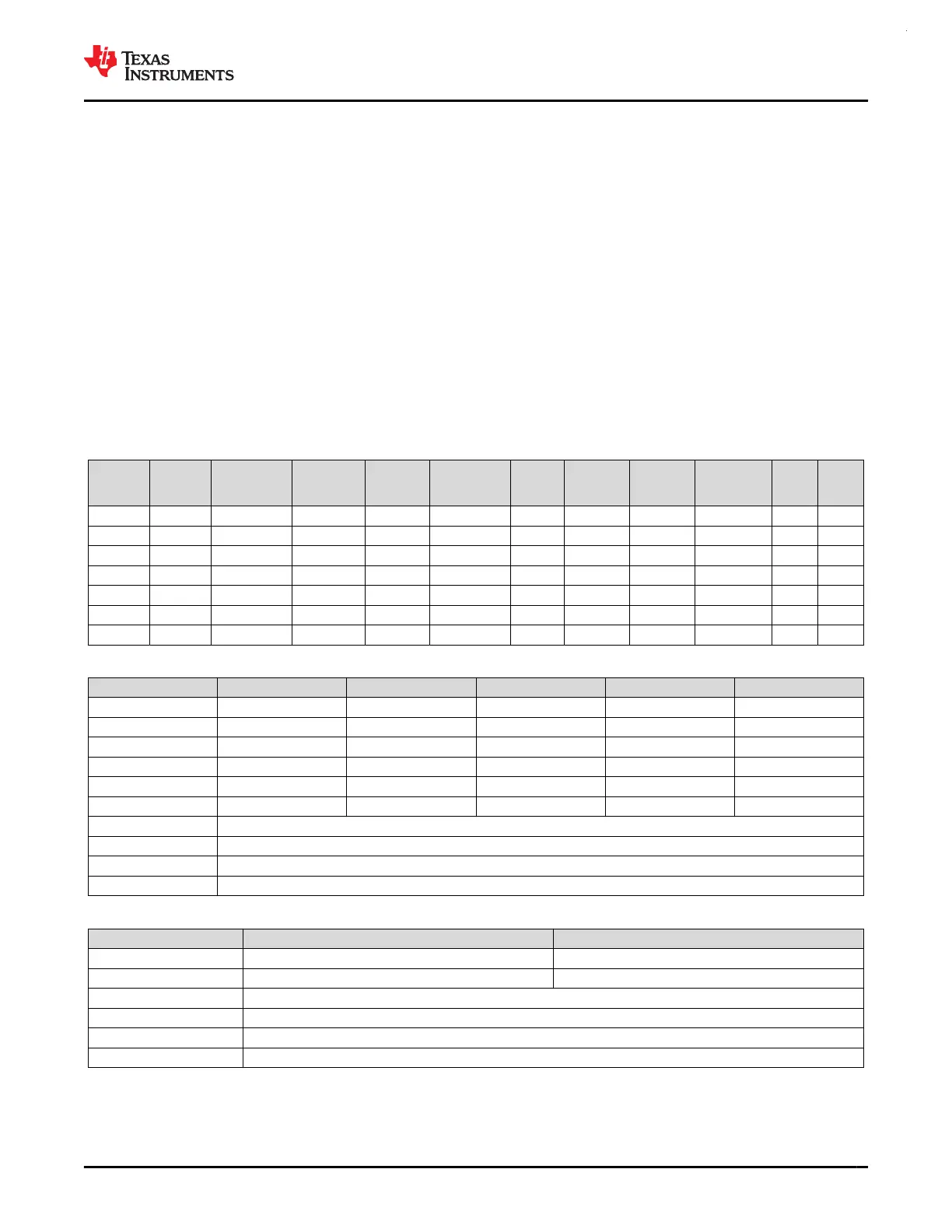

Table 8-15. TIMx Configurations

TIMER

NAME

POWER

DOMAIN

RESOLUTION

PRESCALE

R

REPEAT

COUNTER

CAPTURE /

COMPARE

CHANNELS

PHASE

LOAD

SHADOW

LOAD

SHADOW

CC

DEADBAND FAULT QEI

TIMG0 PD0 16-bit 8-bit – 2 – – – – – –

TIMG6 PD1 16-bit 8-bit – 2 – – – – – –

TIMG7 PD1 16-bit 8-bit – 2 – Yes Yes – – –

TIMG8 PD0 16-bit 8-bit – 2 – – – – – Yes

TIMG12 PD1 32-bit – – 2 – – Yes – – –

TIMA0 PD1 16-bit 8-bit 8-bit 4 Yes Yes Yes Yes Yes –

TIMA1 PD1 16-bit 8-bit 8-bit 2 Yes Yes Yes Yes Yes –

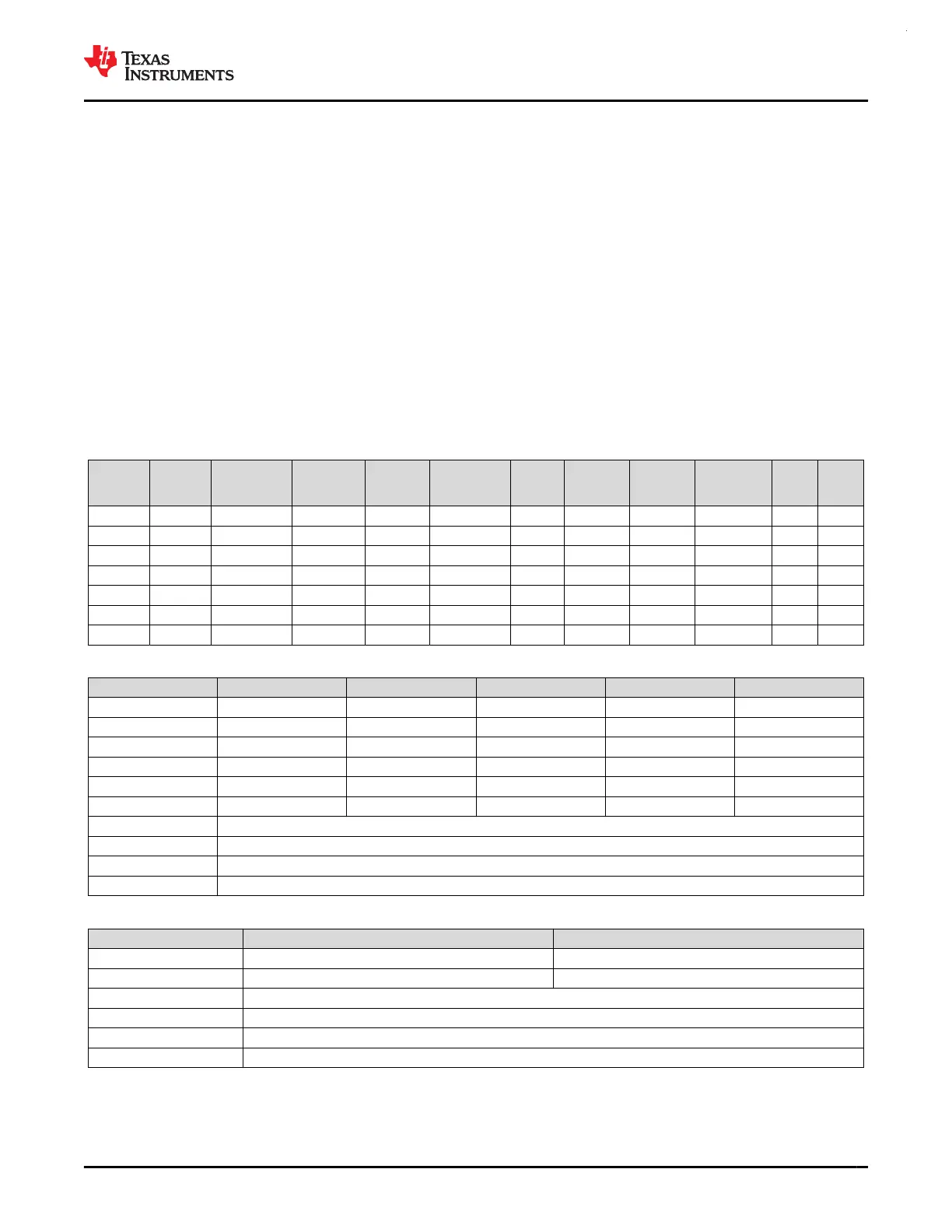

Table 8-16. TIMx Cross Trigger Map (PD1)

TSEL.ETSEL Selection TIMA0 TIMA1 TIMG6 TIMG7 TIMG12

0 TIMA0.TRIG0 TIMA0.TRIG0 TIMA0.TRIG0 TIMA0.TRIG0 TIMA0.TRIG0

1 TIMA1.TRIG0 TIMA1.TRIG0 TIMA1.TRIG0 TIMA1.TRIG0 TIMA1.TRIG0

2 TIMG6.TRIG0 TIMG6.TRIG0 TIMG6.TRIG0 TIMG6.TRIG0 TIMG6.TRIG0

3 TIMG7.TRIG0 TIMG7.TRIG0 TIMG7.TRIG0 TIMG7.TRIG0 TIMG7.TRIG0

4 TIMG12.TRIG0 TIMG12.TRIG0 TIMG12.TRIG0 TIMG12.TRIG0 TIMG12.TRIG0

5 TIMG8.TRIG0 TIMG8.TRIG0 TIMG8.TRIG0 TIMG8.TRIG0 TIMG8.TRIG0

6 to 15 Reserved

16 Event Subscriber Port 0

17 Event Subscriber Port 1

18-31 Reserved

Table 8-17. TIMx Cross Trigger Map (PD0)

TSEL.ETSEL Selection TIMG0 TIMG8

0 TIMG0.TRIG0 TIMG0.TRIG0

1 TIMG8.TRIG0 TIMG8.TRIG0

2 to 15 Reserved

16 Event Subscriber Port 0

17 Event Subscriber Port 1

18-31 Reserved

For more details, see the TIMx chapter of the MSPM0 G-Series 80-MHz Microcontrollers Technical Reference

Manual.

www.ti.com

MSPM0G3507, MSPM0G3506, MSPM0G3505

SLASEX6A – FEBRUARY 2023 – REVISED JUNE 2023

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

69

Product Folder Links: MSPM0G3507 MSPM0G3506 MSPM0G3505

Loading...

Loading...