To

prevent

inadvertent

activation

from disrupting a running

system, the

SCC FUNCTIONS switch is

placed

in

the

DISABLE

positi on.

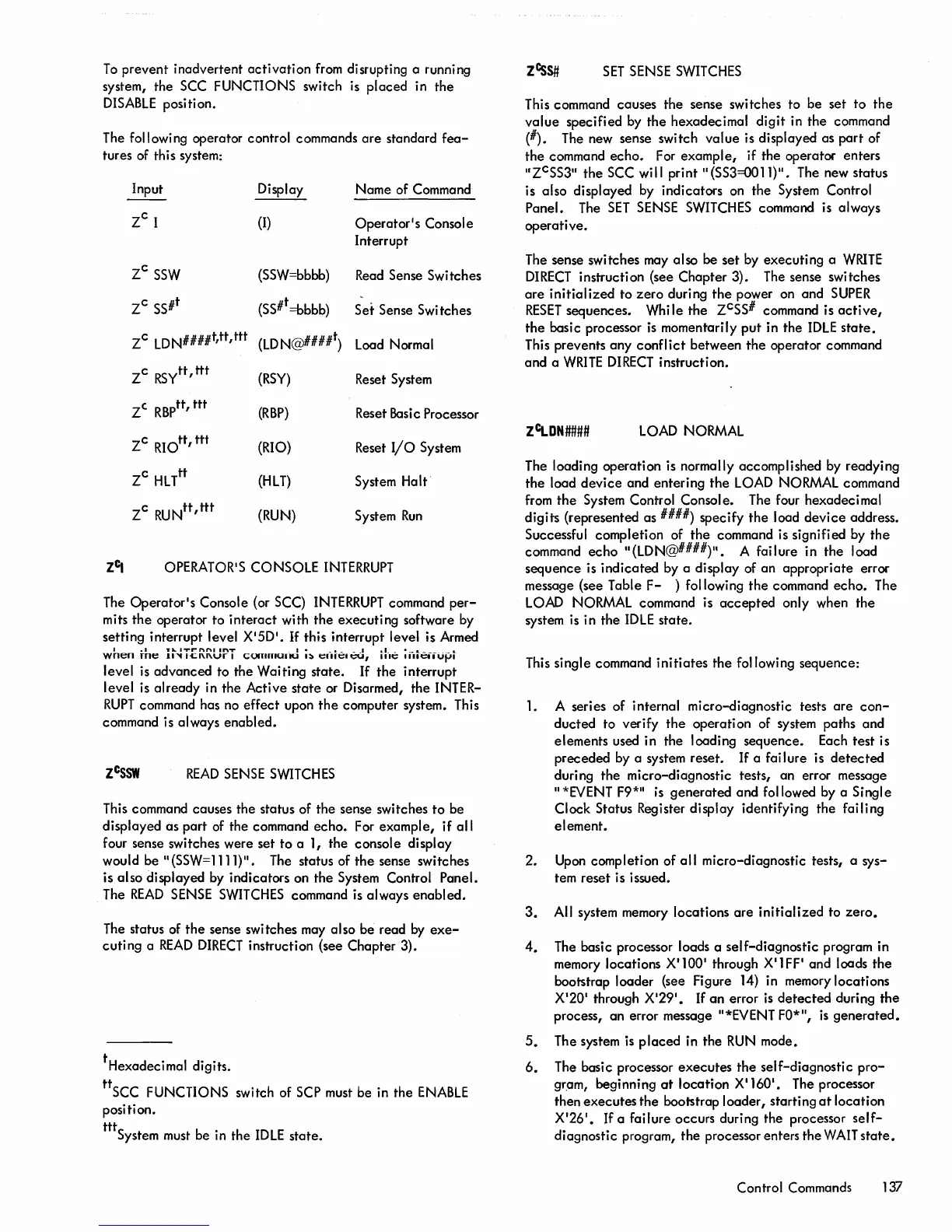

The following operator control commands

are

standard

fea-

tures of th i s system:

Input

Display

Name

of Command

Zc

I

(I)

Operator's

Console

Interrupt

ZC

SSW

(SSW=bbbb)

Read Sense Switches

ZC

ss#t

(Ss#t =bbbb)

Set

Sense

Swi

tches

ZC

LDN####t,tt,ttt

(LDN@####t)

Load Normal

ZC

RSytt,

ttt

(RSY)

Reset System

Ze

RBp

tt

,

ttt

(RBP)

Reset Basic Processor

ZC

RIO

tt

,

ttt

(RIO)

Reset

I/O

System

ZC

HLTtt

(HLT)

System

Halt

ZC

RUN

tt

,

ttt

(RUN)

System

Run

z~

OPERATOR'S CONSOLE

INTERRUPT

The

Operator's

Console (or SCC)

INTERRUPT

command

per-

mits

the

operator

to

interact

with

the

executing

software by

setting

interrupt level X

'

50

'

.

If

this

interrupt

level is Armed

I

.1

.......

ITr-nnllnT

I.

_I

___

I

1.1

__

-

__

L

___

...

_L

wnen

rne

11"1

1i:l\l\vr

I

CQfTIUlUrlU

I~

t:lnt::I~,

lilt::

1I1It::IIUI-'I

level is

advanced

to

the

Waiting

state.

If

the

interrupt

level is

already

in

the

Active

state

or Disarmed,

the

INTER-

RUPT

command has no

effect

upon

the

computer system. This

command is always

enabled.

READ

SENSE

SWITCHES

This command causes

the

status of

the

sense switches

to

be

displayed

as

part

of the command

echo.

For

example,

if

all

four sense switches were

set

to

a 1,

the

console display

would be

II

(SSW=llll)".

The status of

the

sense switches

is

also

displayed by indicators on

the

System Control Panel.

The

READ

SENSE

SWITCHES

command is always

enabled.

The status of

the

sense switches may

also

be read by

exe-

cuting

a

READ

DIRECT

instruction (see

Chapter

3).

tHexadecimal digits.

ttscc

FUNCTIONS switch of SCP must be in

the

ENABLE

position.

ttt

System must be in

the

ID

LE

state.

zCSsn

SET

SENSE

SWITCHES

This command causes

the

sense switches

to

be

set

to

the

value

specified

by

the

hexadecimal

digit

in

the

command

(#). The new sense switch

value

is displayed as

part

of

the

command

echo.

For

example,

if

the

operator

enters

uZcSS3"

the

SCC will

print

II

(SS3=O0l1)". The new status

is also displayed by

indicators

on

the

System Control

Panel. The

SET

SENSE

SWITCHES

command is

always

operative.

The sense switches may also be

set

by

executing

a

WRITE

DIRECT

instruction (see

Chapter

3). The sense switches

are

initialized

to

zero

during

the

power on

and

SUPER

RESET

sequences.

While

the

ZcSS# command is

active,

the

basic processor

is

momentarily

put

in

the

IDLE

state.

This prevents

any

conflict

between

the

operator command

and

a

WRITE

DIRECT

instruction.

Zct.ON####

LOAD NORMAL

The loading

operation

is normally accomplished by readying

the

load

device

and

entering

the

LOAD NORMAL command

from

the

System Control Console. The four hexadecimal

digits

(represented as ####) specify

the

load

device

address.

Successful

completion

of

the

command is signified by

the

command

echo

II{LDN@####)II. A

failure

in

the

load

sequence

is

indicated

by a display of

an

appropriate

error

message (see Table

F-

) following

the

command

echo.

The

LOAD NORMAL command is

accepted

only when

the

system is in

the

IDLE

state.

This single command

initiates

the

following sequence:

1.

A series of internal micro-diagnostic tests

are

con-

ducted

to verify

the

operati on of system paths

and

elements used

in

the

loading

sequence.

Each

test

is

preceded

by a system reset.

If

a

failure

is

detected

during

the

micro-diagnostic

tests,

an

error message

II

*EVENT F9*"

is

generated

and

followed by a

Single

Clock Status Register display identifying

the

failing

element.

2.

Upon completion

of

all

micro-diagnostic tests, a sys-

tem

reset

is issued.

3.

All system memory locations

are

initialized

to

zero.

4.

The basic processor loads a

self-diagnostic

program in

memory locations

X

'

l00

'

through X

'

1FF

'

and

loads

the

bootstrap loader (see Figure 14) in memory locations

X

'

20

'

through

X'29

1

•

If

an

error

is

detected

during

the

process,

an

error message "*EVENT FO*",

is

generated.

5.

The system

is

placed

in

the

RUN

mode.

6.

The basic processor

executes

the

self-diagnostic

pro-

gr,am, beginning

at

location

X'l60

'

•

The processor

then

executes

the

bootstrap

loader,

starting

at

location

X'26

1

•

If

a failure occurs during

the

processor

self-

diagnostic program,

the

processor enters

the

WAIT

state.

Control Commands 137

Loading...

Loading...