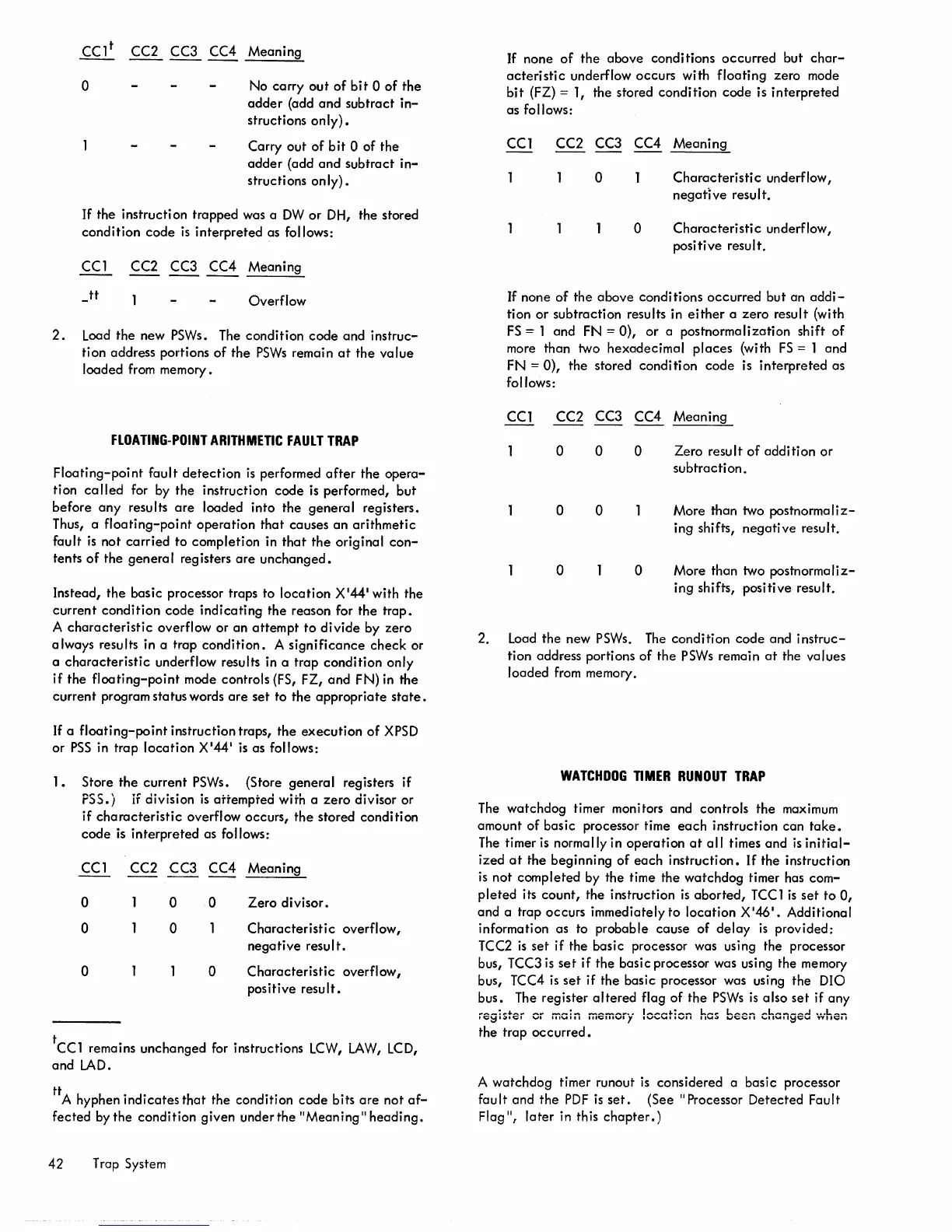

CClt

CC2 CC3 CC4 Meaning

o No carry

out

of

bit

0

of

the

adder

(add

and

subtract

in-

structions

only).

Carry

out

of

bit

0 of the

adder

(add

and

subtract

in-

structions

only).

If

the instruction trapped was a

OW

or

DH, the stored

condition

code

is

interpreted

as follows:

CCl

CC2 CC3

CC4

Meaning

Overflow

2.

Load

the

new PSWs. The condition

code

and instruc-

tion address portions

of

the

PSWs

remain

at

the

value

loaded from memory.

FLOATING-POINT

ARITHMETIC

FAULT

TRAP

Floating-point

fault

detection

is

performed

after

the

opera-

tion

called

for by

the

instruction

code

is

performed,

but

before

any

results

are

loaded into

the

general

registers.

Thus, a

floating-point

operation

that

causes

an

arithmetic

fault

is

not

carried

to

completion in

that

the

original

con-

tents

of

the

genera

I reg isters

are

unchanged.

Instead,

the

basic processor traps to

location

X

'

44

1

with the

current

condition

code

indicating

the reason for

the

trap.

A

characteristic

overflow or

an

attempt

to

divide

by

zero

always results in a trap

condition.

A

significance

check

or

a

characteristic

underflow results in a

trap

condition

only

if

the

floating-point

mode controls (FS, FZ,

and

FN) in the

current

program status words

are

set

to

the

appropriate

state.

If

a

floating-point

instruction traps,

the

execution

of

XPSD

or

PSS

in trap

location

X

'

44

1

is

as follows:

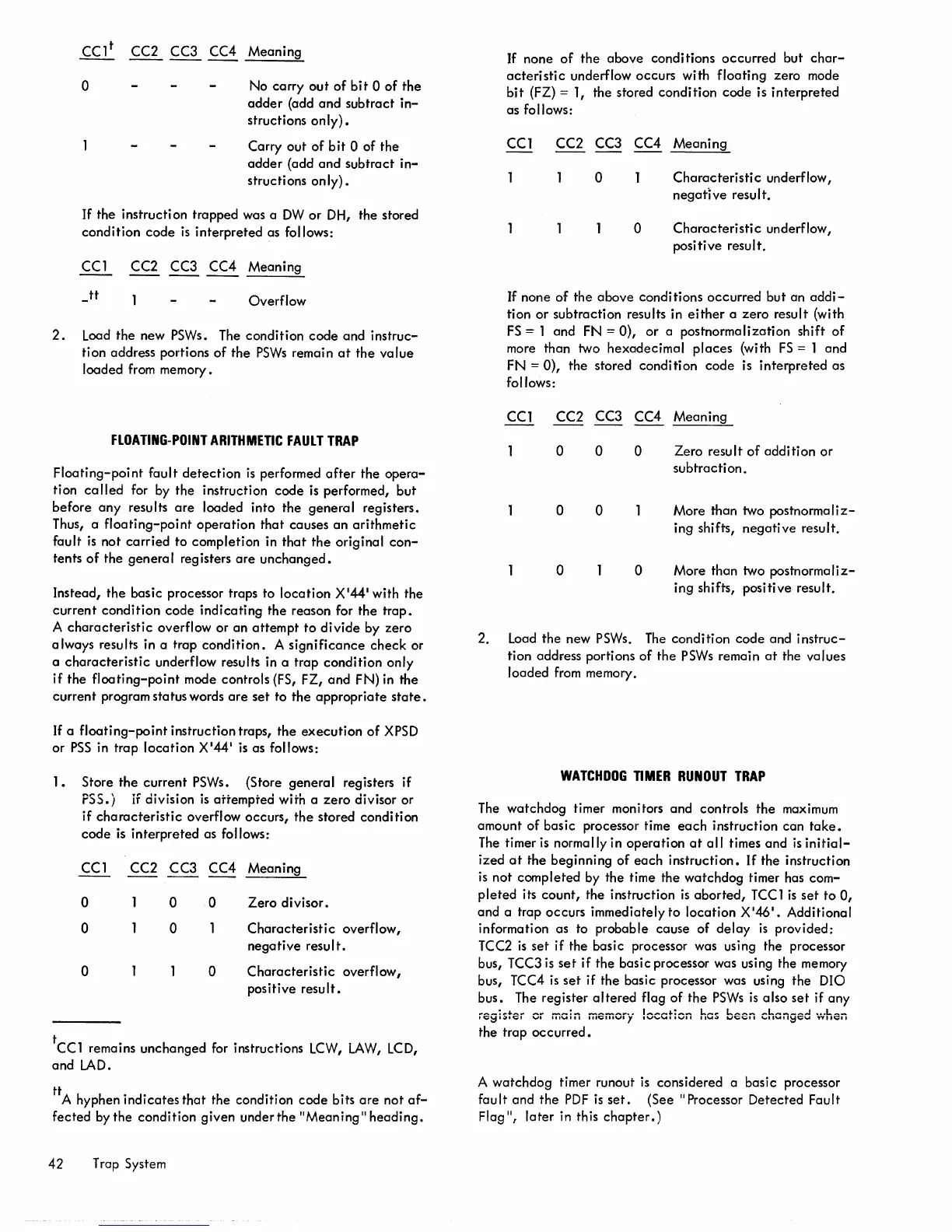

1.

Store

the

current

PSWs. (Store

general

registers

if

r:>:>.) if division

is

aTtempted with a

zero

divisor or

if

characteristic

overflow occurs,

the

stored condition

code

is

interpreted

as follows:

CCl

CC2

CC3

CC4

Meaning

0 0

0

Zero

divisor.

0 0

Characteristic

overflow,

negative

result.

0

0

Characteristic

overflow,

positive

result.

tCCl

remains unchanged for instructions

LCW,

LAW,

LCD,

and

LAD.

ttA hyphen

indicates

that

the condition

code

bits

are

not

af-

fected

by the

condition

given

under the

"Meaning"heading.

42 Trap System

2.

If

none

of

the

above

condi tions

occurred

but

char-

acteristic

underflow

occurs

with

floating

zero

mode

bit

(FZ) = 1, the stored

condition

code

is

interpreted

as follows:

CCl

CC2

CC3 CC4

Meaning

o

o

Characteristic

underflow,

negative

result.

Characteri

sti c underflow,

positive result.

If

none

of

the

above

conditions

occurred

but an

addi-

tion

or

subtraction results in

either

a

zero

result (with

FS

= 1

and

FN = 0),

or

a postnormalization shift

of

more than two hexadecimal

places

(with

FS

= 1

and

FN =

0),

the stored

condition

code

is

interpreted

as

follows:

CCl

CC2

CC3 CC4

Meaning

o

o

o o

o

o

o

Zero result

of

addition

or

subtraction.

More than two

postnormaliz-

ing shifts,

negative

result.

More than two

postnormaliz-

ing shifts, positive result.

Load

the

new

PSWs.

The

condition

code

and

instruc-

tion address portions

of

the

PSWs

remain

at

the values

loaded from memory.

WATCHDOG

TIMER

RUNOUT

TRAP

The

watchdog

timer monitors

and

controls

the

maximum

amount

of

basic processor time

each

instruction

can

take.

The timer

is

normally in

operation

at

all

times

and

is

initial-

ized

at

the beginning

of

each

instruction.

If the instruction

is

not completed by the time the watchdog timer has

com-

pleted

its

count,

the instruction

is

aborted,

TCCl

is

set

to

0,

and

a trap occurs immediately

to

location

X

'

46

I

•

Additional

information

as

to probable cause of

delay

is

provided:

TCC2

is

set

if the basic processor was using the processor

bus,

TCC3

is

set

if

the basic processor was using the memory

bus,

TCC4

is

set

if

the basic processor was using

the

DIO

bus. The register

altered

flag

of

the

PSWs

is

also

set

if

any

register

or

main memory !occt:on

has

beeil changed

Vvheii

the

trap

occurred.

A

watchdog

timer runout

is

considered a basic processor

fault

and

the

PDF

is

set.

(See

II

Processor

Detected

Fault

Flag",

later

in this

chapter.)

Loading...

Loading...