Instruction Name

Mnemonic

Divide Word

DW

Add Word to Memory

AWM

Modi fy and Test Byte

MTS

Modify and Test Halfword

MTH

Modify and Test Word

MTW

The

fixed-point

arithmetic

instruction

set

performs binary

addition,

subtraction,

multiplication,

and division with

integer

operands

that

may be

data,

addresses,

index

values,

or

counts.

One

operand may

be

either

in the instruction

word

itself

or

may be in

one

or

two

of

the

current

general

registers;

the

second operand may be

either

in main memory

or

in

one

or

two

of

the

current

general

registers. For most

of

these instructions, both operands may be in the same

general

register, thus permitting the doubling, squaring,

or

clearing

the contents

of

a register by using a

reference

address

value

equal to the R field

value.

All

fixed-point

arithmetic

instructions provide a condition

code

setti

ng

that

i ndi

cates

the fo Ilowi ng information

about

the result

of

the

operation

called

for by the instruction:

Condition

code

settings:

2 3 4 Result

o 0 ·Zero - the result in the specified

general

register(s)

is

all zeros.

-

0

Negative

- the instruction has produced a

fixed-point

negative

result.

o Positive - the instruction has produced a

fj xed

-po

in t positi ve resu It.

- 0

Fixed-point

overflow has not

occurred

during

execution

of

an

add,

subtract,

or

divide

in-

struction, and

the

result is

correct.

o

Fixed-point

overflow has

occurred

during

execution

of

an

add,

subtract,

or

divide

in-

struction. For

addition

and

subtraction,

the

incorrect

result

is

loaded into the designated

register{s}. For a

divide

instruction, the

designated register(s), and

CC1, CC3, and

CC4

are

not

affected.

No carry - for an add

or

subtract

instruction,

there was

no

carry

of

a

l-bit

out

of

the

high-

order (sign)

bit

position

of

the

result.

- Carry - for an add

or

subtract

instruction,

there was a

l-bit

carry

out

of

the sign

bit

position

of

the result. (Subtracting

zero

wi

II

a Iways produce carry. )

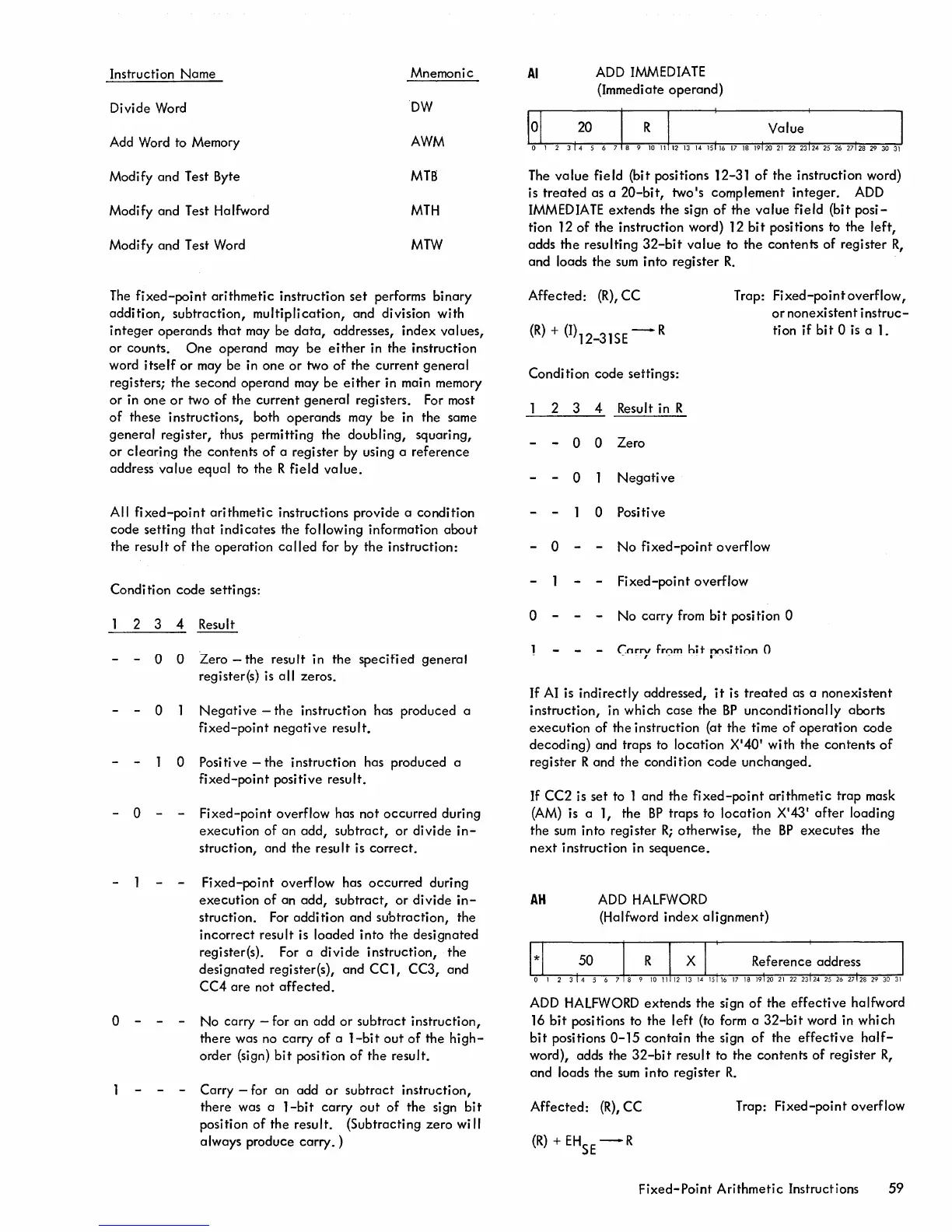

AI

ADD

IMMEDIATE

{Immediate operand}

20

o 1 2

The

value

field (bit positions 12-31

of

the instruction word)

is

treated

as a

20-bit,

two's complement

integer.

ADD

IMMEDIATE

extends

the

sign

of

the

value

field (bit

posi-

tion 12

of

the instruction word) 12

bit

positions to the left,

adds

the

resulting

32-bit

value

to the contents of register

R,

and loads the

sum

into regi

ster

R.

Affected:

(R),

CC

(R)

+ (I)12-31SE - R

Condition

code

settings:

2 3 4 Result in R

-

0 0 Zero

- 0

Negative

o Positive

Trap:

Fixed-point

overflow,

or

nonexistent

instruc-

tion if

bit

0 is a

1.

- 0

No

fixed-point

overflow

Fixed-point

overflow

o

No

carry

from

bit

position 0

-

l.nrrv

frnm

hit

noc;itinn

0

- - I - - - -

,--

If AI is

indirectly

addressed,

it

is

treated

as a nonexistent

instruction, in which

case

the

BP

unconditionally

aborts

execution

of the instruction (at the time

of

operation

code

decoding)

and traps to location

X'40'

with the contents

of

register R and the condition

code

unchanged.

If CC2 is

set

to 1 and

the

fixed-point

arithmetic

trap mask

(AM)

is

a 1, the

BP

traps to

location

X'43'

after

loading

the

sum

into register

R;

otherwise, the

BP

executes

the

next

instruction in

sequence.

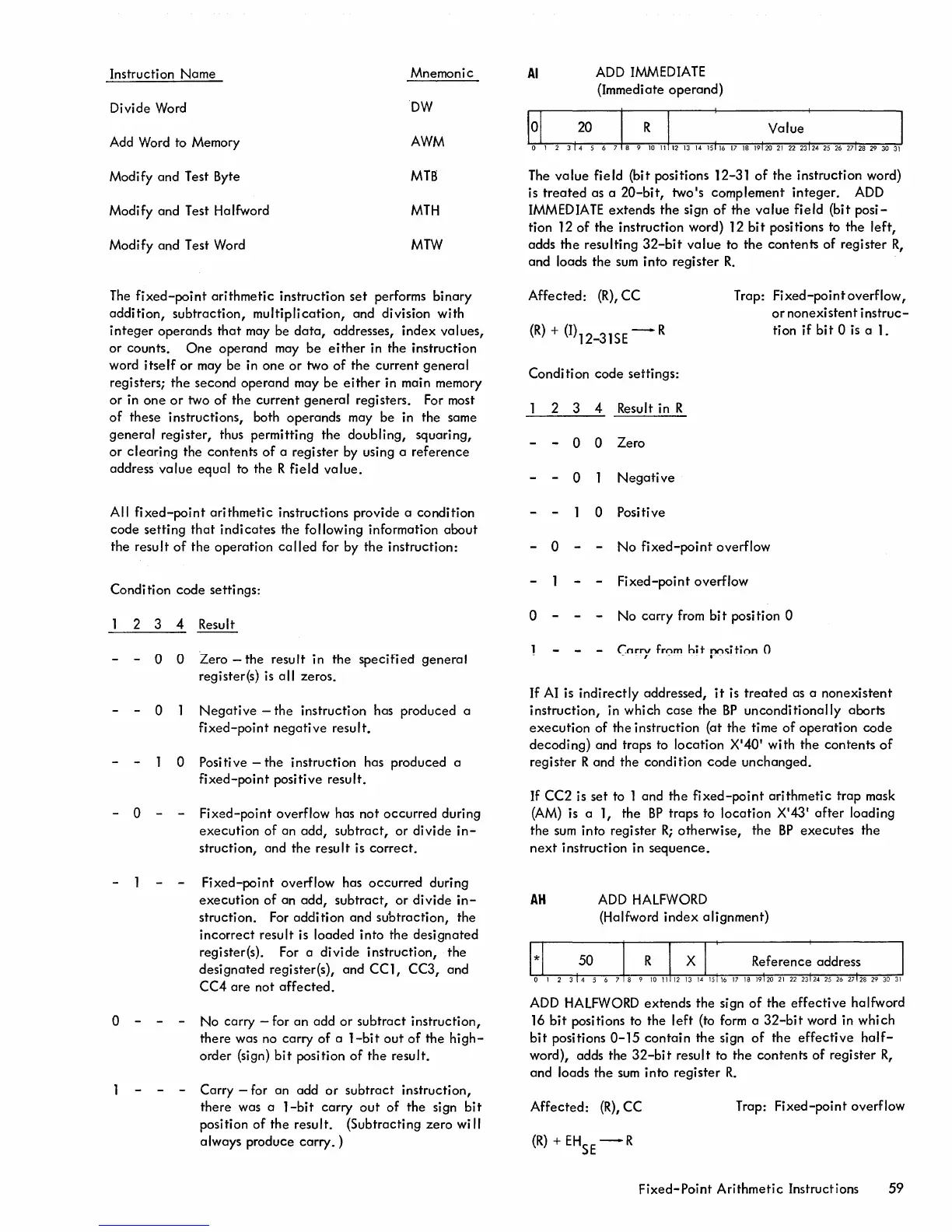

AH

ADD

HALFWORD

(Halfword

index

alignment)

ADD

HALFWORD

extends

the sign

of

the

effective

halfword

16

bit

positions to the

left

(to form a

32-bit

word in

which

bit

positions

0-15

contain

the sign

of

the

effective

half-

word), adds the

32-bit

result to

the

contents

of

register

R,

and loads

the

sum

into register

R.

Affected:

(R),

CC

Trap:

Fixed-point

overflow

(R)

+

EHSE-R

Fixed-Point

Arithmetic

Instructions

59

Loading...

Loading...