62 www.xilinx.com VC709 Evaluation Board

UG887 (v1.0) February 4, 2013

Chapter 1: VC709 Evaluation Board Features

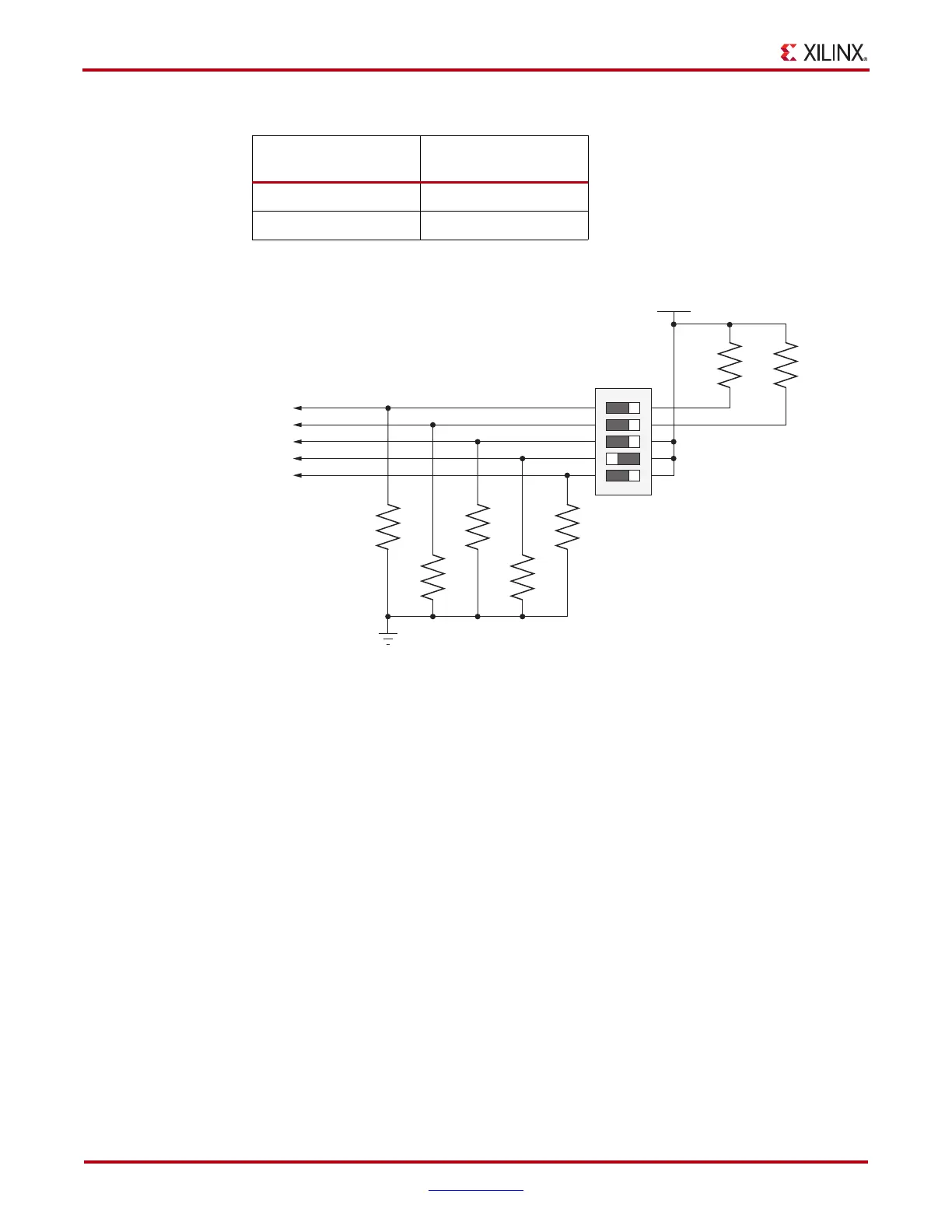

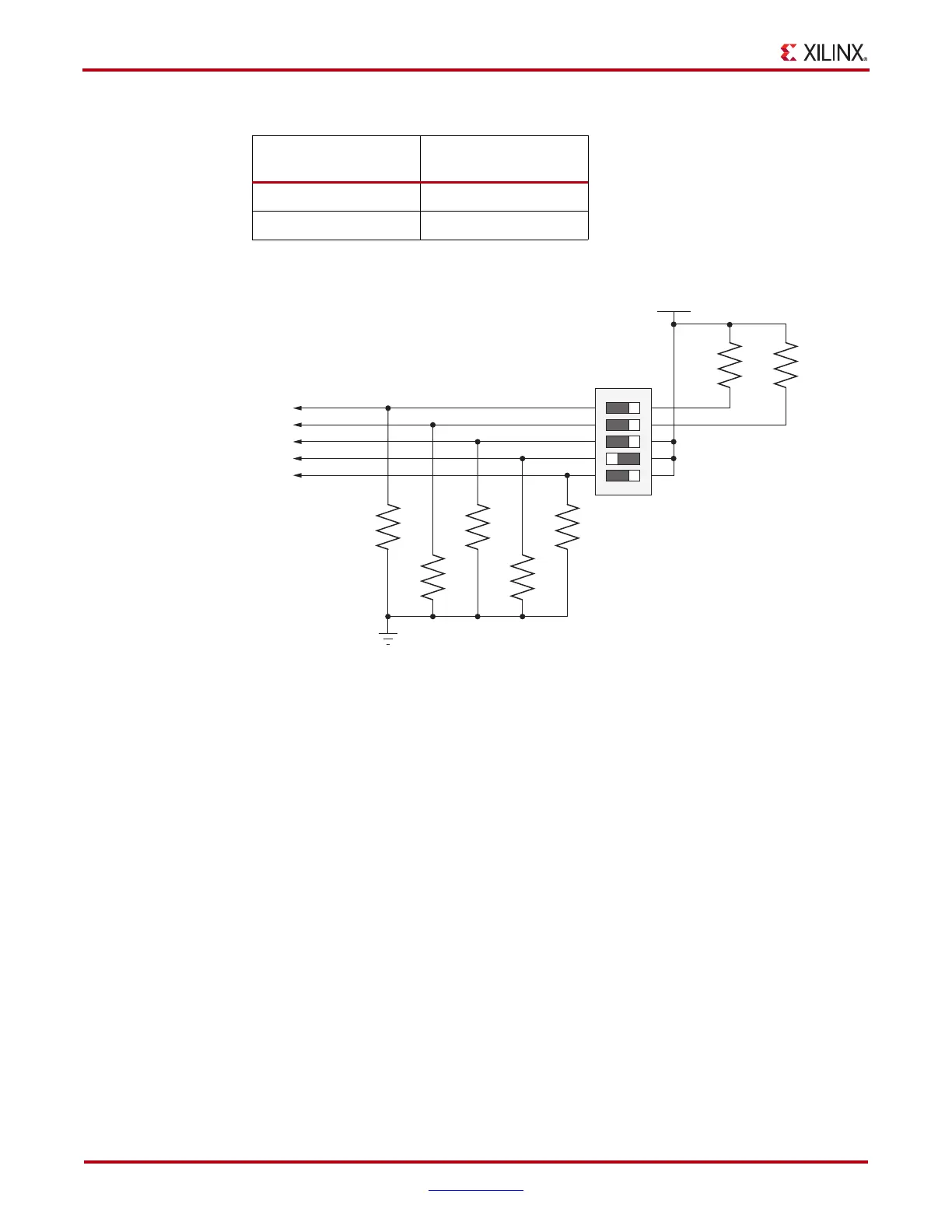

Figure 1-27 shows mode switch SW13.

The mode pins settings on SW11 determine if the linear BPI flash is used for configuring

the FPGA. DIP switch. SW11 also provides the upper two address bits for the linear BPI

flash and can be used to select one of multiple stored configuration bitstreams. Figure 1-28

shows the connectivity between the onboard nonvolatile flash devices used for

configuration and the FPGA.

To obtain the fastest configuration speed, an external 80 MHz oscillator is wired to the

EMCCLK pin of the FPGA. This allows users to create bitstreams that configure the FPGA

over the 16-bit datapath from the linear BPI flash memory at a maximum synchronous

read rate of 40 MHz. The bitstream stored in the flash memory must be generated with a

BitGen option to divide the EMCCLK by two.

Table 1-26: Mode Switch SW11 Settings

Mode Pins

(M2, M1, M0)

Configuration Mode

010 Master BPI

101 JTAG

X-Ref Target - Figure 1-27

Figure 1-27: Mode Switch

UG887_c1_27_090612

SDA05H1SBD

SW11

R401

220Ω

0.1 W

1%

R402

220Ω

0.1 W

1%

VCC2V5

FPGA_M2

FPGA_M1

FPGA_M0

FLASH_A25

FLASH_A24

R396

1.21kΩ

0.1 W

1%

R397

1.21kΩ

0.1 W

1%

R398

1.21kΩ

0.1 W

1%

R399

1.21kΩ

0.1 W

1%

R400

1.21kΩ

0.1 W

1%

1

2

3

4

5

10

9

8

7

6

GND

ON

Loading...

Loading...