Embedded Tri-Mode Ethernet MAC User Guide www.xilinx.com 165

UG074 (v2.2) February 22, 2010

Interfacing to an FPGA Fabric-Based Statistics Block

R

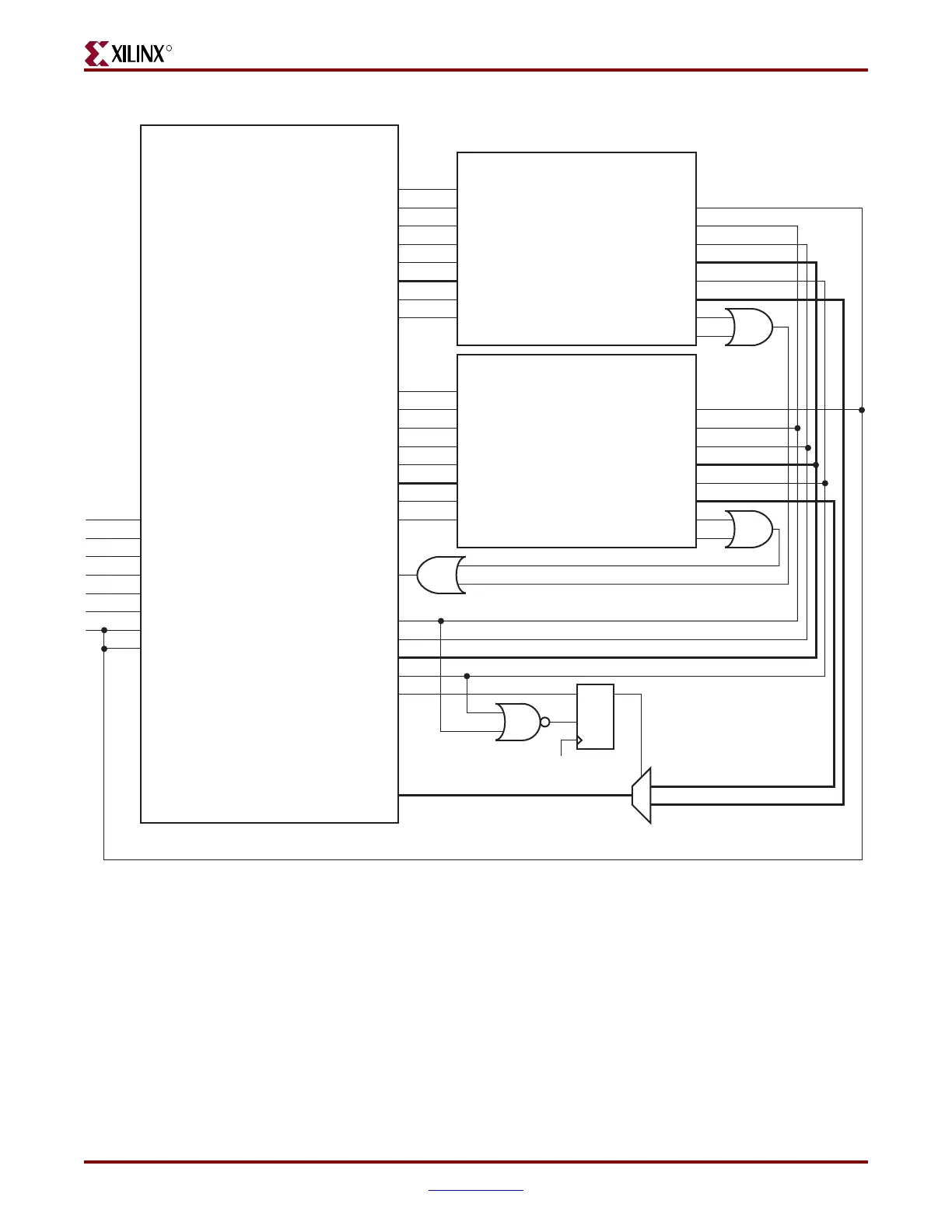

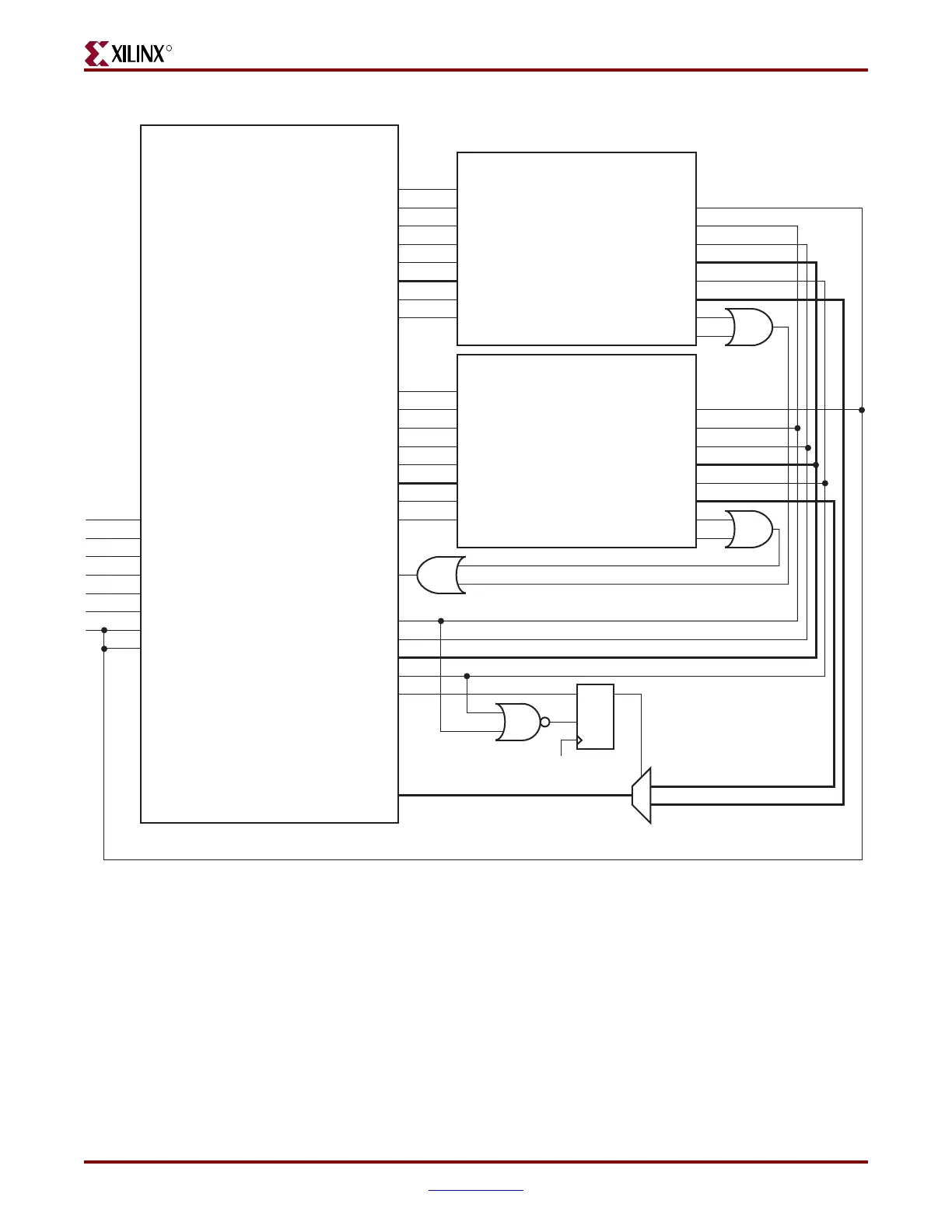

Figure 6-3: DCR Bus to Ethernet Statistics Connection

Virtex-4 FPGA Embedded

Tri-Mode Ethernet MAC

HOSTMIIMRDY

HOSTMIIMSEL

HOSTWRDATA[31:0]

CLIENTEMAC1TXCLIENTCLKIN

EMAC1CLIENTTXSTATS

EMAC1CLIENTTXSTATSVLD

CLIENTEMAC1RXCLIENTCLKIN

EMAC1CLIENTRXSTATS[6:0]

EMAC1CLIENTRXSTATSVLD

EMAC1CLIENTRXSTATSBYTEVLD

EMAC1CLIENTTXSTATSBYTEVLD

LogiCORE Ethernet Statistics

Example Design

host_clk

host_addr[8:0]

host_addr[9]

host_req

host_miim_sel

host_rd_data[31:0]

txclientclkin

clienttxstats

clienttxstatsvld

rxclientclkin

clienttxstatsvld[6:0]

clientrxstatsvld

clienttxstatsbyte

valid

clientrxstatsbytevalid

CLIENTEMAC0TXCLIENTCLKIN

EMAC0CLIENTTXSTATS

EMAC0CLIENTTXSTATSVLD

CLIENTEMAC0RXCLIENTCLKIN

EMAC0CLIENTRXSTATS[6:0]

EMAC0CLIENTRXSTATSVLD

EMAC0CLIENTRXSTATSBYTEVLD

EMAC0CLIENTTXSTATSBYTEVLD

LogiCORE Ethernet Statistics

Example Design

host_clk

host_addr[8:0]

host_addr[9]

host_req

host_miim_sel

host_rd_data[31:0]

txclientclkin

clienttxstats

clienttxstatsvld

rxclientclkin

clienttxstatsvld[6:0]

clientrxstatsvld

clienttxstatsbytevalid

clientrxstatsbytevalid

DCRREAD

DCRDINBUS

DCRACK

DCRRDBUS

DCRWRITE

DCRABUS

DCRCLK

host_stats_msw_rdy

host_stats_lsw_rdy

host_stats_msw_rdy

host_stats_lsw_rdy

OR

OR

OR

HOSTRDDATA[8:0]

HOSTRDDATA[15]

HOSTRDDATA[9]

1

0

HOSTRDDATA[10]

EN

NOR

DQ

DCRCLK

UG074_4_03_012408

HOSTCLK

Loading...

Loading...