93

Using the 81110A/81104A

T

TT

Th

hh

he

e e

e P

PP

Pa

aa

at

tt

tt

tt

te

ee

er

rr

rn

n n

n S

SS

Sc

cc

cr

rr

re

ee

ee

ee

en

nn

n

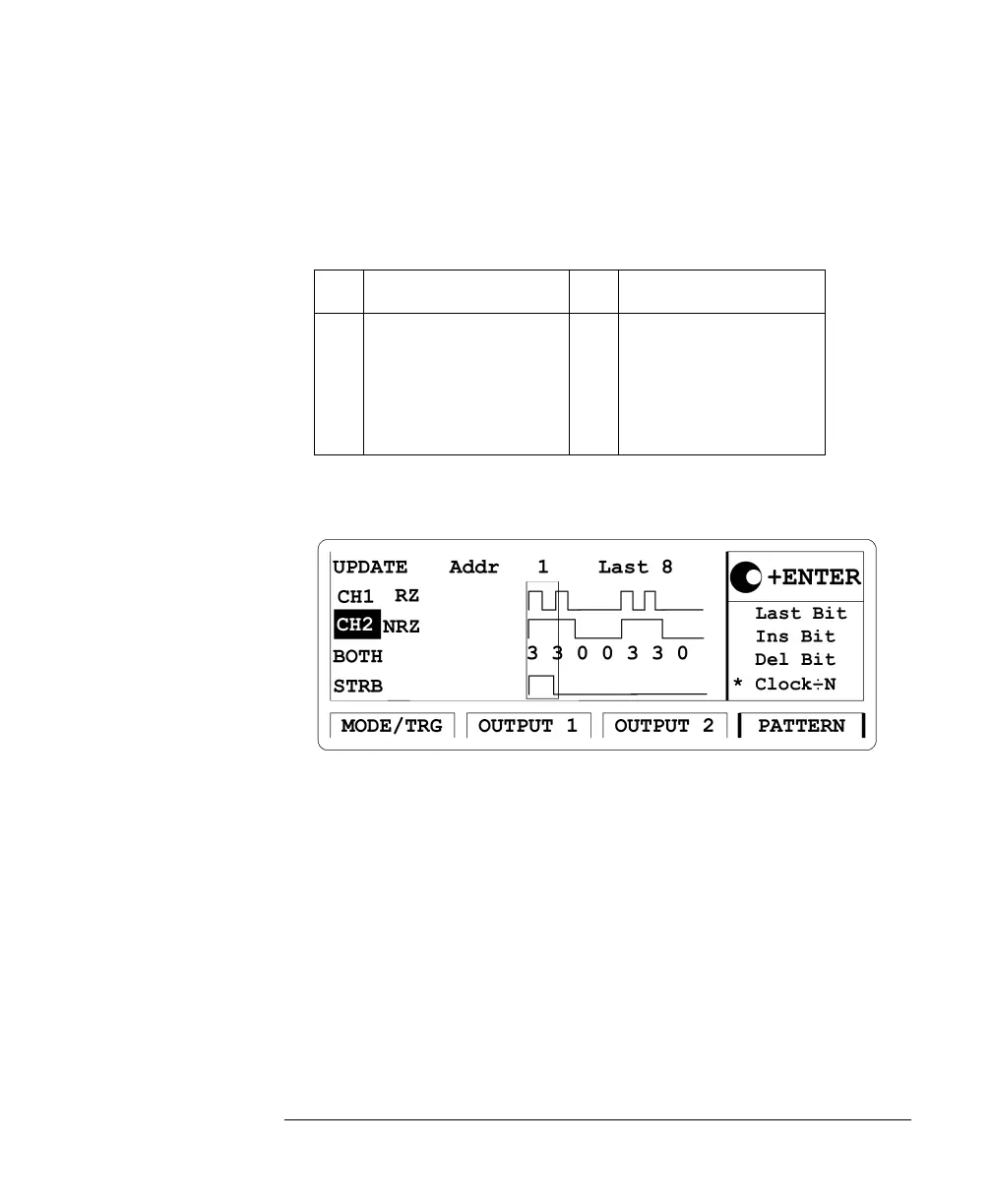

C

LOCK

÷N

Fill bits A

DDR

to L

AST

with a divided clock pattern. After pressing

ENTER you can adjust the dividing factor from 2 to 16384 and press

ENTER again to implement.

Note that the output signal is only a square wave if you are using NRZ

data. You can see this best in graphics mode:

PRBS 2

N

-1

Fill bits A

DDR

to L

AST

with a 2

n

-1 Pseudo-random Binary Sequence.

After pressing ENTER you can adjust n in the range 7 to 14 and press

ENTER again to implement.

n Sequence n Sequence

2 101010101010101... 6 111000111000111...

3 100100100100100... 7 111000011100001...

4 110011001100110... 8 111100001111000...

5 110001100011000...

Loading...

Loading...