Publication 1747-RM001G-EN-P - November 2008

11-28 Understanding Interrupt Routines

Interrupt Subroutine (ISR) Content

The Interrupt Subroutine (INT) instruction should be the first instruction in

your ISR. This identifies the subroutine file as an I/O interrupt subroutine.

The ISR contains the rungs of your application logic. You can program any

instruction inside an ISR except a TND, REF, or SVC instruction. IIM or

IOM instructions are needed in an ISR if your application requires immediate

update of input or output points. Terminate the ISR with an RET (return)

instruction.

JSR stack depth is limited to 3. That is, you may call other subroutines to a

level 3 deep from an ISR.

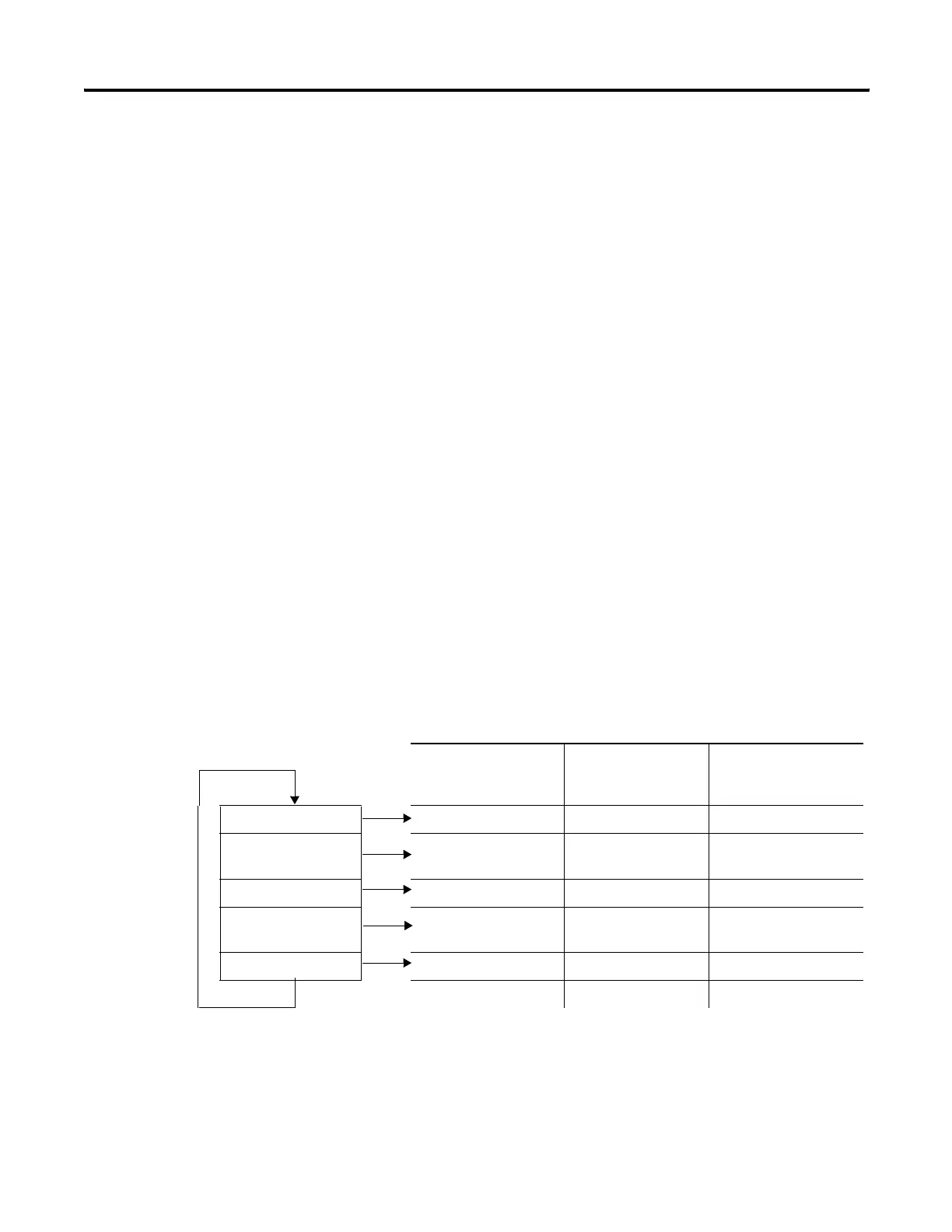

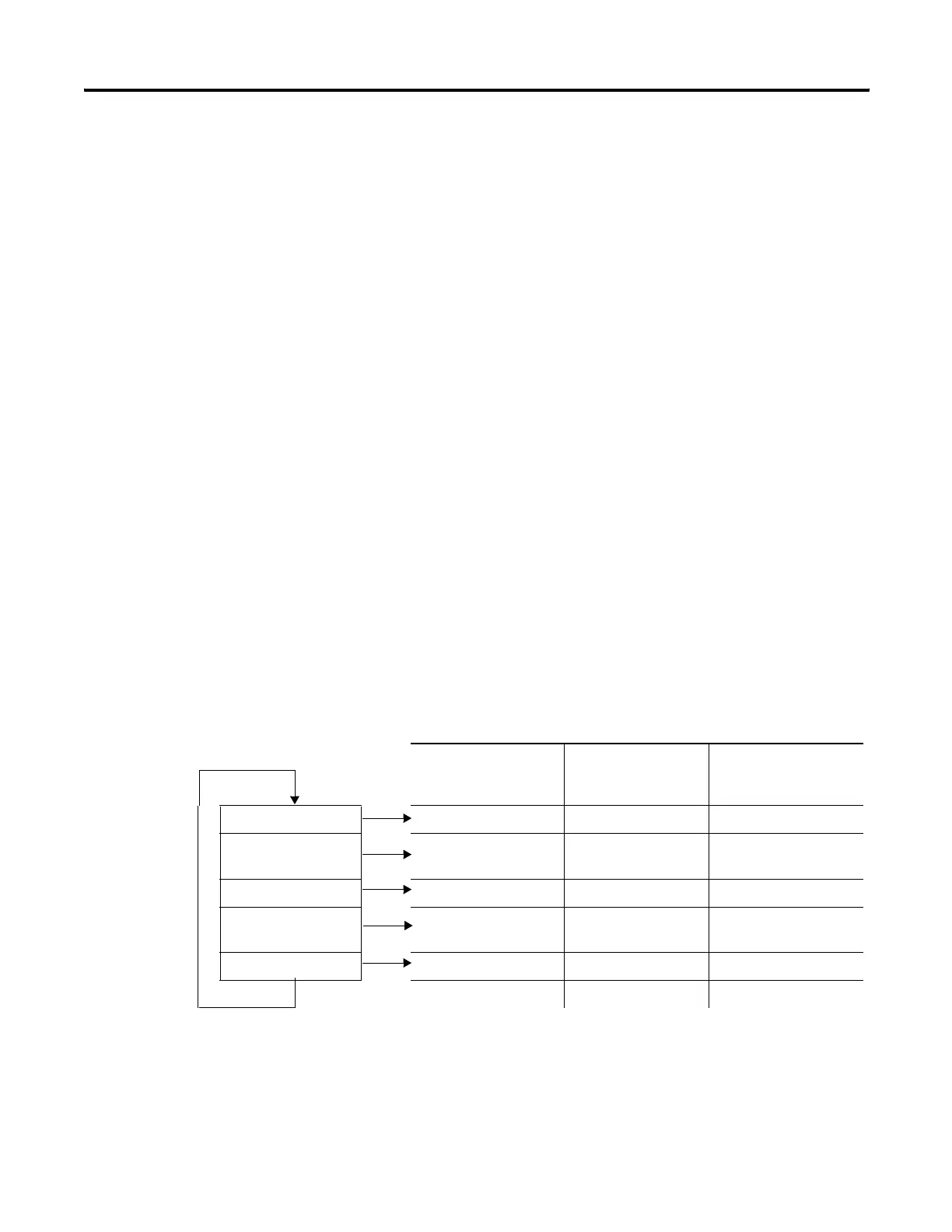

Interrupt Latency and Interrupt Occurrences

Interrupt latency is the interval between the I/O module’s request for service

and the start of the interrupt subroutine. I/O interrupts can occur at any point

in your program, but not necessarily at the same point on successive

interrupts. Interrupts can only occur between instructions in your program,

inside the I/O scan (between slots), or between the servicing of

communication packets. The following table shows the interaction between an

interrupt and the processor operating cycle.

Note that ISR execution time adds directly to the overall scan time. During the

latency period, the processor is performing operations that cannot be

disturbed by the ISR interrupt function.

SLC 5/02 I/O Interrupts 5/03 and Higher I/O

Interrupts with Bit

S:33/8 set

5/03 and Higher I/O

Interrupts with Bit

S:33/8 cleared

Input Scan Between slot updates Between word updates Between slot updates

Program Scan Between instruction

updates

Between word updates Between rung updates

Output Scan Between slot updates Between word updates Between slot updates

Communications Between communication

packets

Between word packet

updates

Between communication

packets

Processor Overhead At start and end Between word updates Between word updates

Events in the Processor Operating Cycle

Loading...

Loading...