Publication 1747-RM001G-EN-P - November 2008

4-10 Math Instructions

Updates to the Math Registers, S:13 and S:14

During integer operation, the unrounded quotient is placed in the most

significant word (S:14), the remainder is placed in the least significant word

(S:13).

Example

The remainder of 11/2 is 0.5, so the quotient is rounded up to 6 and is stored

in the destination. The unrounded quotient, which is 5, is stored in S:14 and

the remainder, which is 1, is stored at S:13.

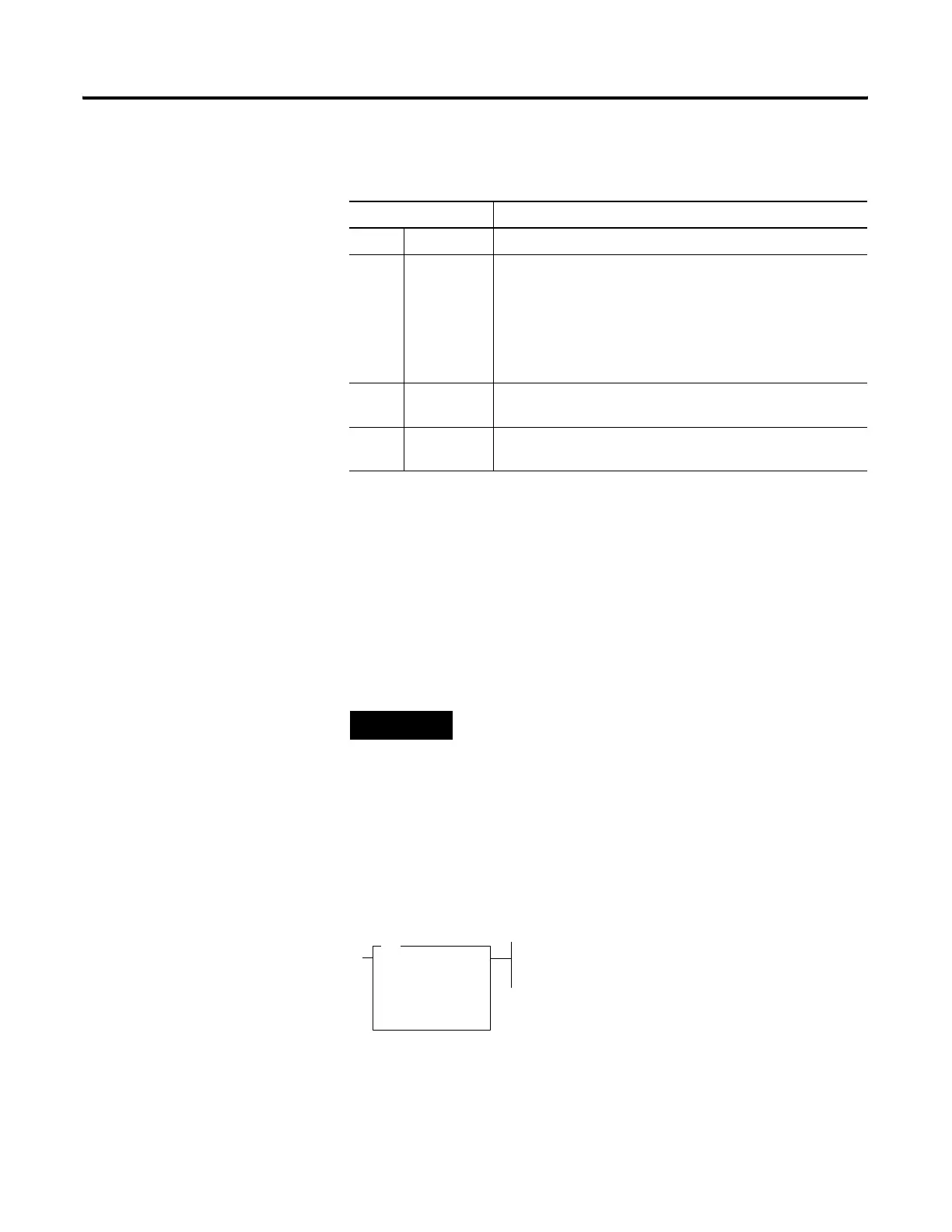

Table 4.8 Processor Function

With this Bit The Processor

S:0/0 Carry (C) always resets.

S:0/1 Overflow (V) sets if division by zero or overflow is detected; otherwise resets.

On overflow, the minor error flag is also set. The value 32,767 is

placed in the destination. Exception: If you are using an SLC1

5/02 or higher processor and have S:2/14 (math overflow

selection bit) set, then the unsigned, truncated overflow remains

in the destination. For floating point destinations, the overflow

result remains in the destination.

S:0/2 Zero (Z) sets if result is zero; otherwise resets; undefined if overflow is

set.

S:0/3 Sign (S) sets if result is negative; otherwise resets; undefined if overflow

is set.

TIP

For floating point operation, the math register does

not change.

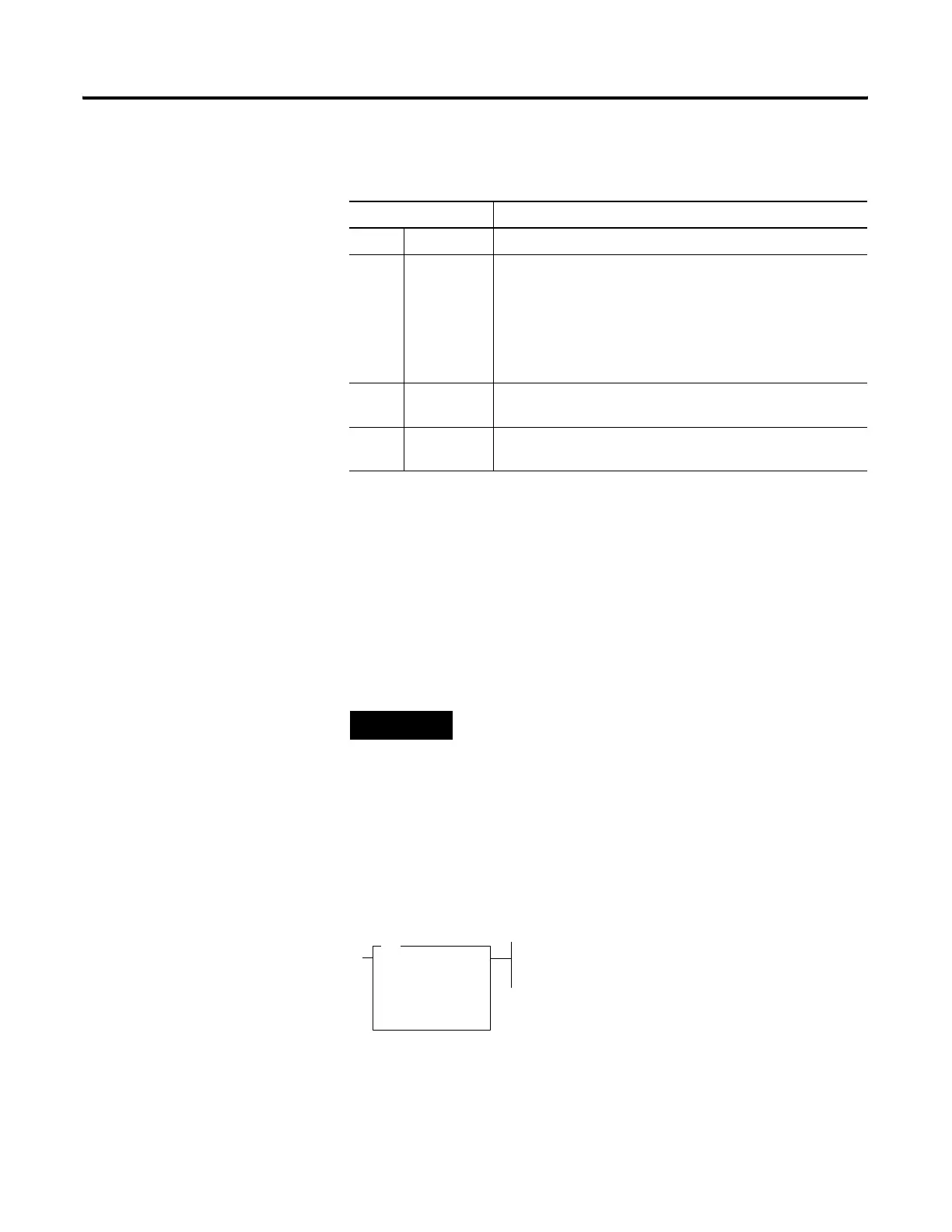

DIV

DIVIDE

Source A N7:0

11

Source B N7:1

2

Dest N7:2

6

where: N7:0 = 11

N7:1 = 2

N7:2 = 6

result: S:14 = 5

S:13 = 1

Loading...

Loading...