The MPSoC device and the flash devices can be configured via JTAG from Xilinx SDK or Xilinx Vivado Hard-

ware Manager - for this operation, the ARM DAP must be enabled.

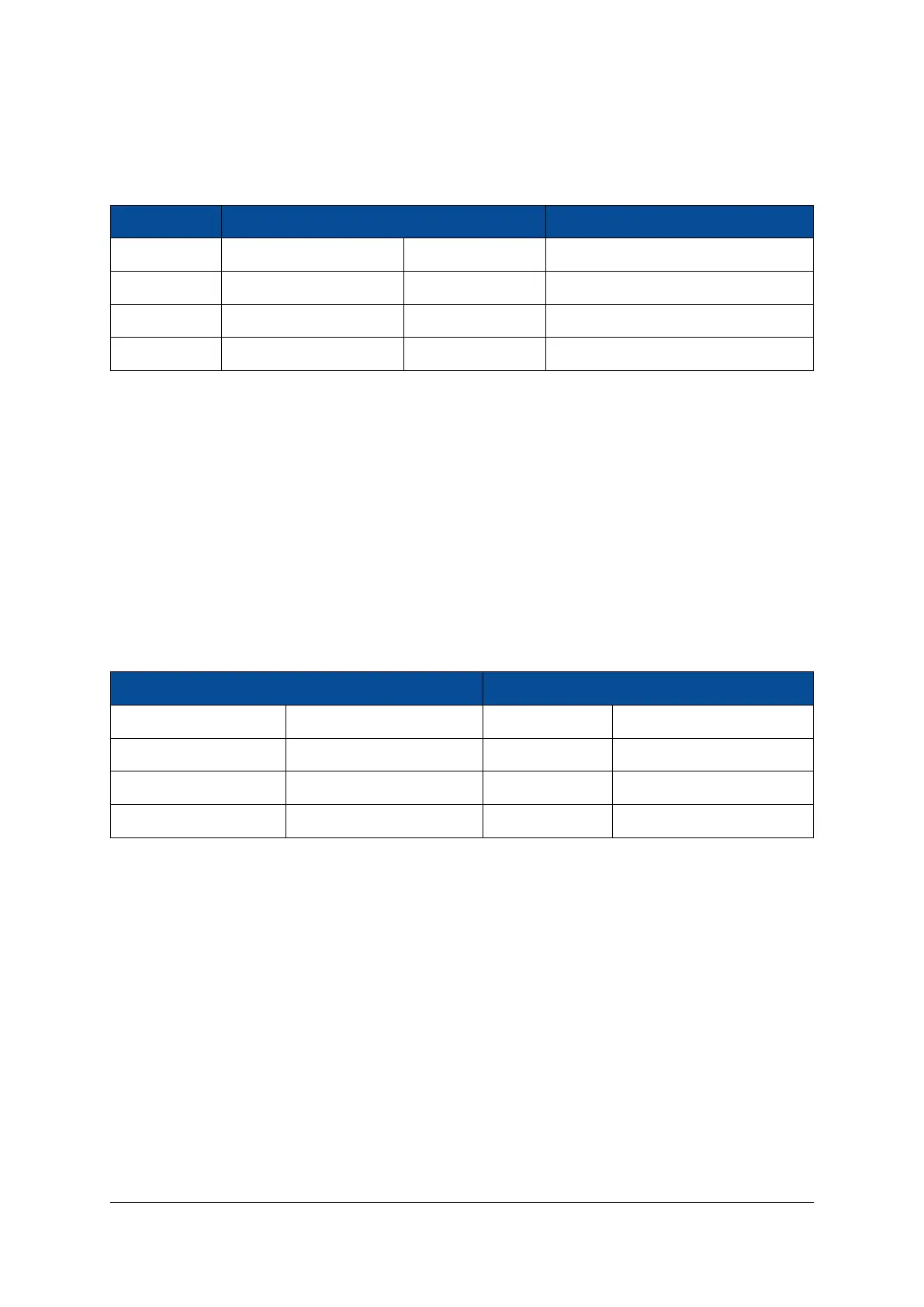

Signal Name Module Connector Pin PS Dedicated Pin Resistor

JTAG_TCK A-123 PS_JTAG_TCK 10 kΩ pull-up to VCC_CFG_MIO

JTAG_TMS A-119 PS_JTAG_TMS 10 kΩ pull-up to VCC_CFG_MIO

JTAG_TDI A-117 PS_JTAG_TDI 10 kΩ pull-up to VCC_CFG_MIO

JTAG_TDO A-121 PS_JTAG_TDO 10 kΩ pull-up to VCC_CFG_MIO

Table 39: JTAG Interface - PL and PS Access and Debug

3.6.2 External Connectivity

JTAG signals can be connected directly on the base board to a JTAG connector. No pull-up/pull-down re-

sistors are necessary. The VREF pin of the programmer must be connected to VCC_CFG_MIO.

It is recommended to add 22 Ω series termination resistors between the module and the JTAG header, close

to the source. Please refer to the Enclustra Module Pin Connection Guidelines for details on JTAG interface.

3.6.3 PJTAG on Debug Connector

The JTAG pins available on the debug connector are used by the ARM DAP for debugging the PS. These

pins can be used when the ARM DAP is not on the JTAG chain.

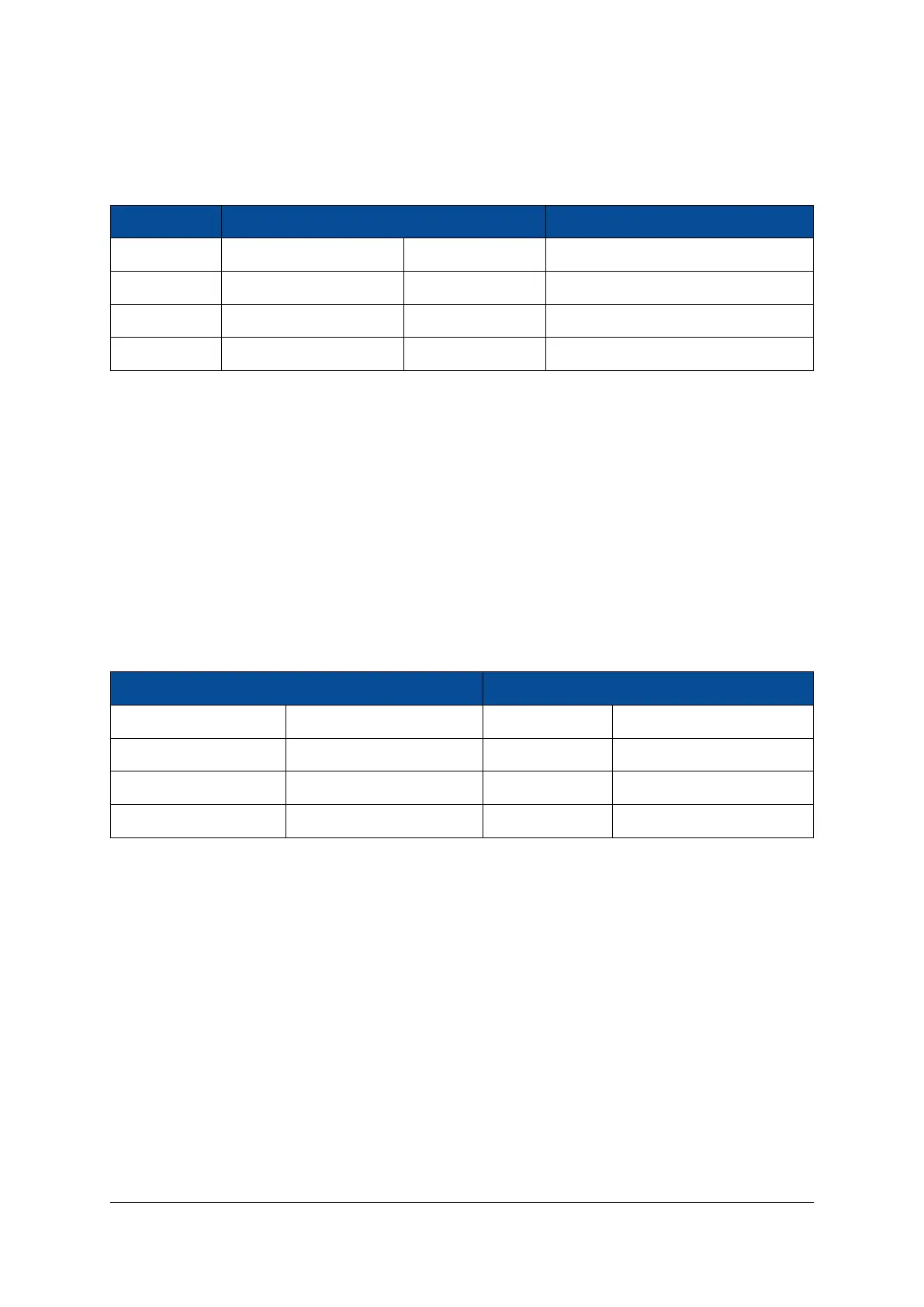

Signal Name Pin on Debug Connector PS Pin Resistor

I2C_INT#_PJTAG_TCK 3 MIO12 51.7 kΩ pull-up to VCC_3V3

EMMC_IO2_PJTAG_TMS 1 MIO15 47 kΩ pull-up to VCC_1V8

EMMC_IO0_PJTAG_TDI 7 MIO13 47 kΩ pull-up to VCC_1V8

EMMC_IO1_PJTAG_TDO 9 MIO14 47 kΩ pull-up to VCC_1V8

Table 40: JTAG Interface - ARM DAP Access via PJTAG Signals (valid only for modules revision 1 and 2)

In the standard configuration, PJTAG boot mode is not supported. In order to enable the PJTAG boot mode

via MIO pins 12-15 (PJTAG1 pins), PJTAG_EN# must be driven low from pin 2 of the optional debug connector.

Note that starting with revision 3, the debug connector is not offered as an optional feature anymore. The

related circuitry has been completely removed, including the MIO pin mappings for PJTAG, TRACE, and

debug UART interfaces. PJTAG boot mode is also not supported any longer. The signals that were mapped

to the debug connector have been renamed to reflect these changes.

3.6.4 JTAG Boot Mode

Starting with revision 4, support for JTAG boot mode has been added to increase the usability of the module

with Xilinx tools, for example for QSPI flash programming or FPGA bitstream loading.

The following steps are required in order to boot the module in JTAG mode:

• Set the boot mode selection signals for QSPI boot

D-0000-428-001 53 / 66 Version 13, 15.08.2019

Loading...

Loading...