2 Module Description

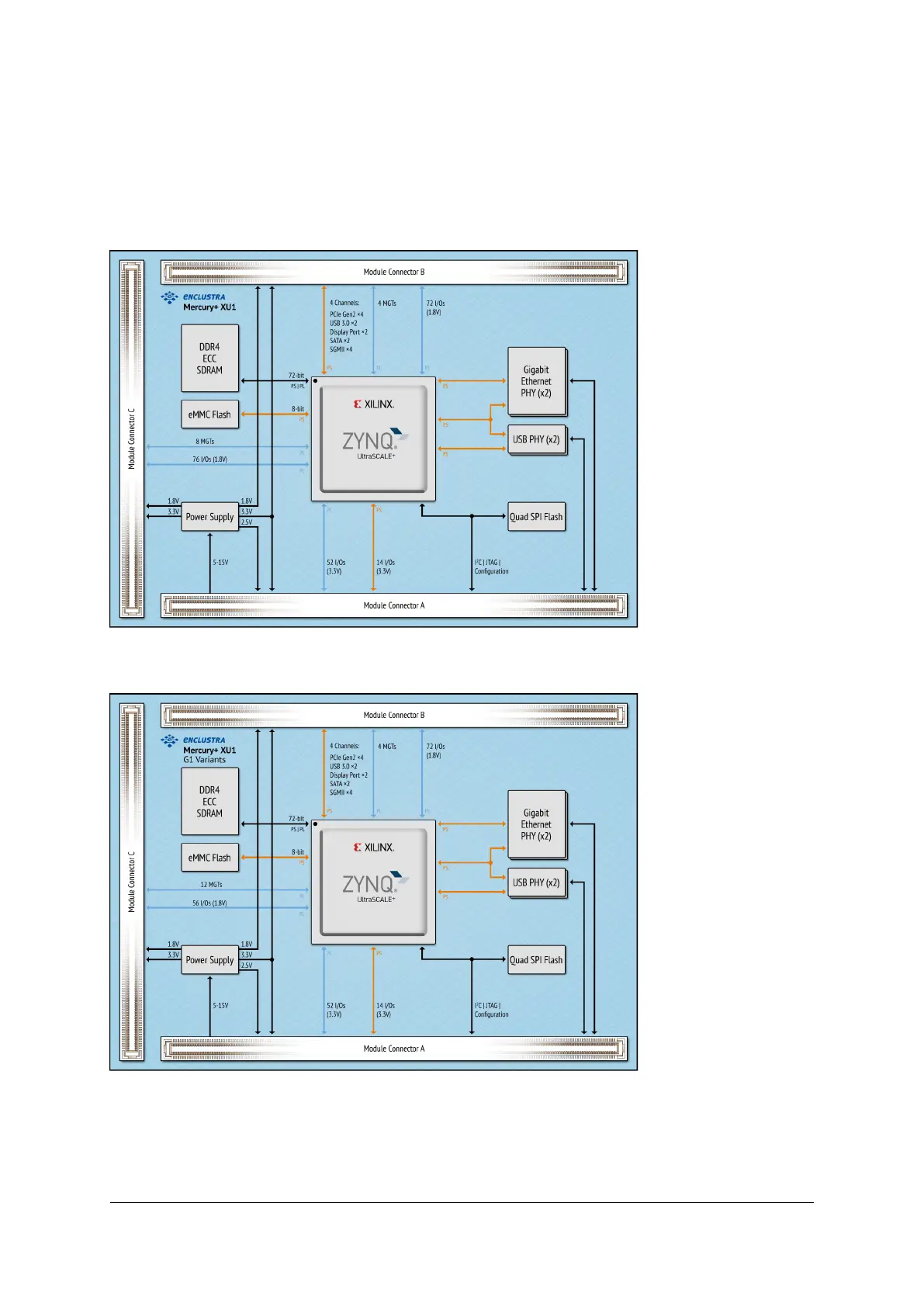

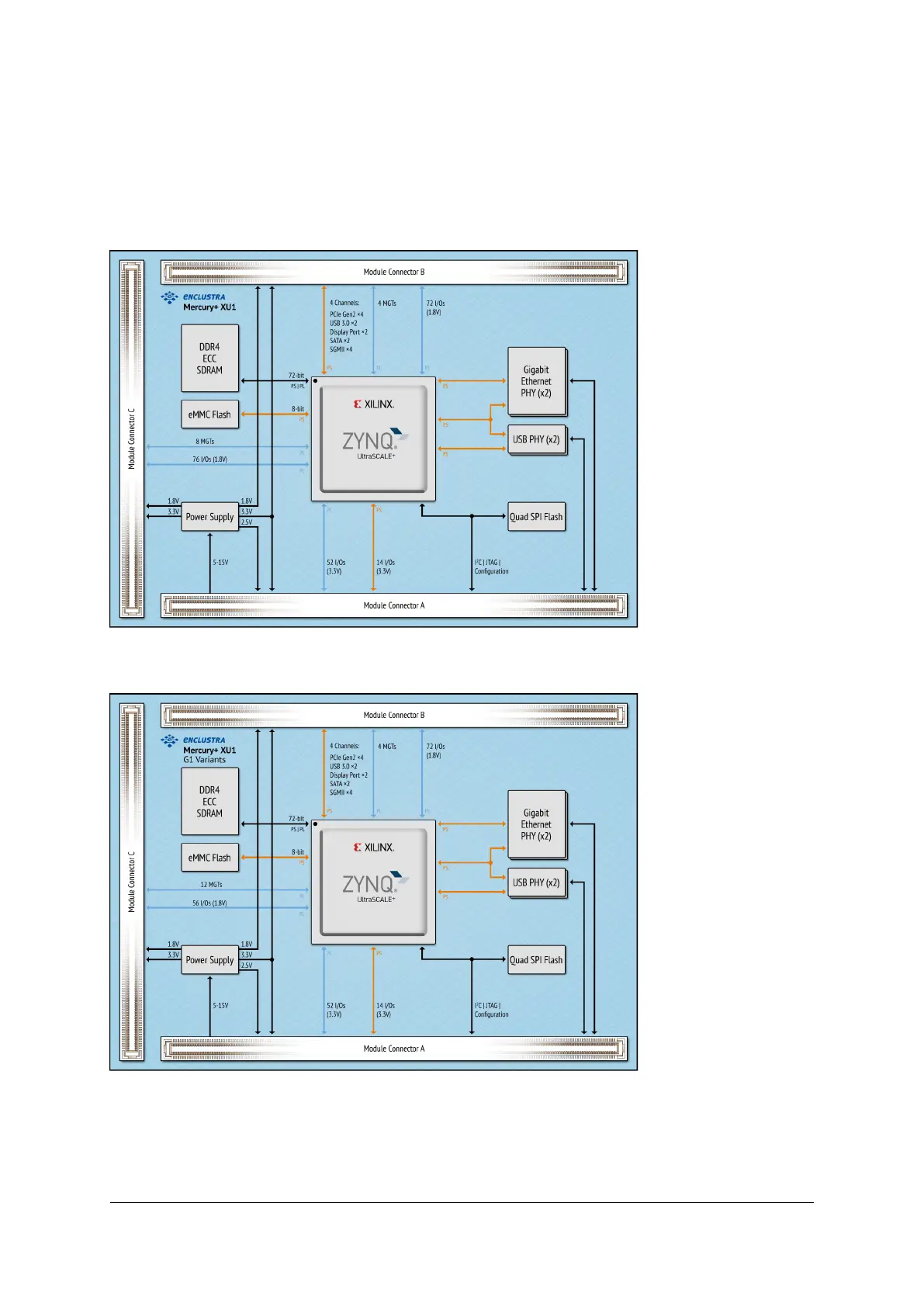

2.1 Block Diagram

Figure 1: Hardware Block Diagram

Figure 2: Hardware Block Diagram - G1 Variants

The main component of the Mercury+ XU1 SoC module is the Xilinx Zynq Ultrascale+ MPSoC device. Most

of its I/O pins are connected to the Mercury+ module connector, making up to 214 regular user I/Os avail-

able to the user. Further, up to twenty MGT pairs are available on the module connector, making possible the

D-0000-428-001 10 / 66 Version 13, 15.08.2019

Loading...

Loading...