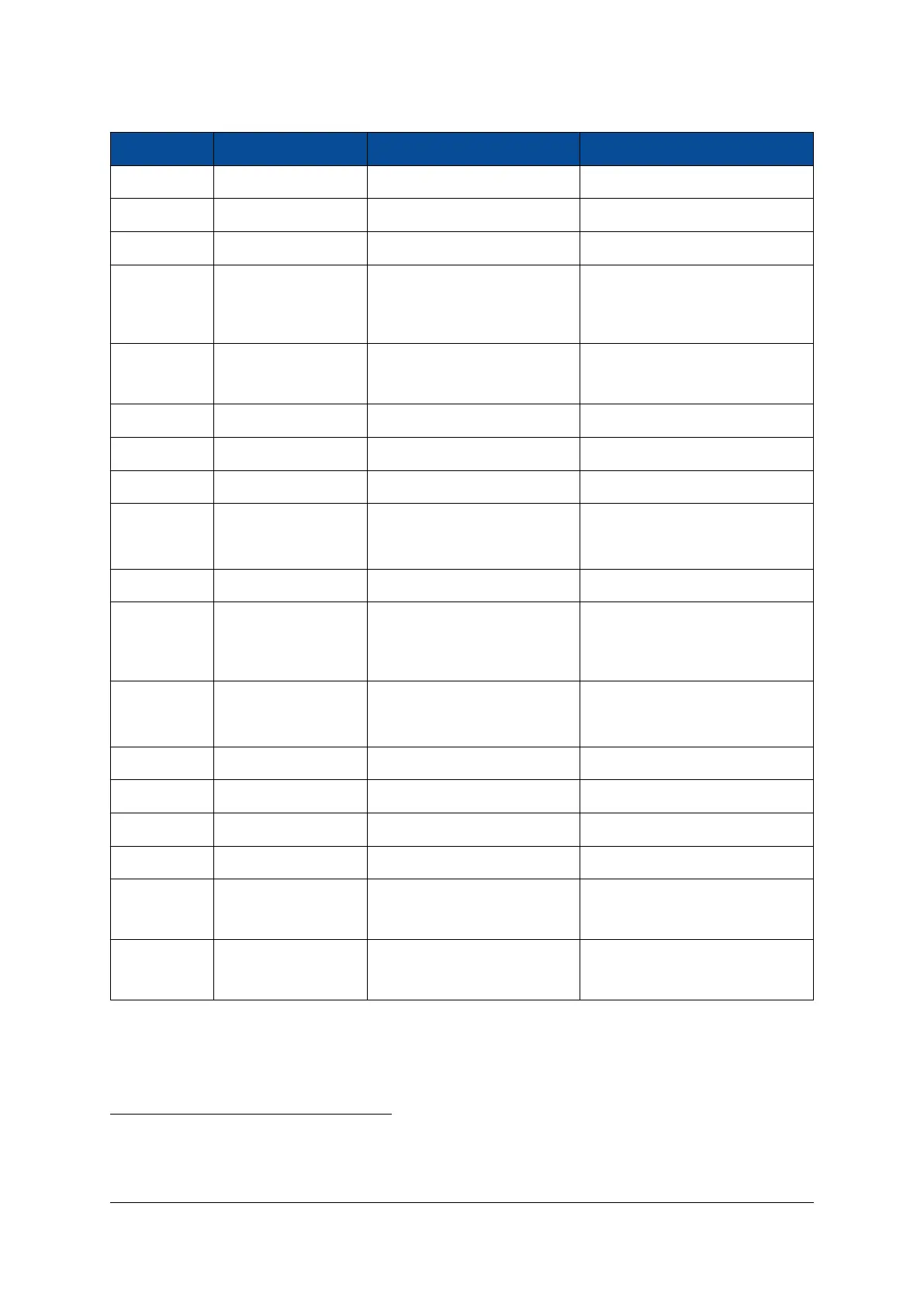

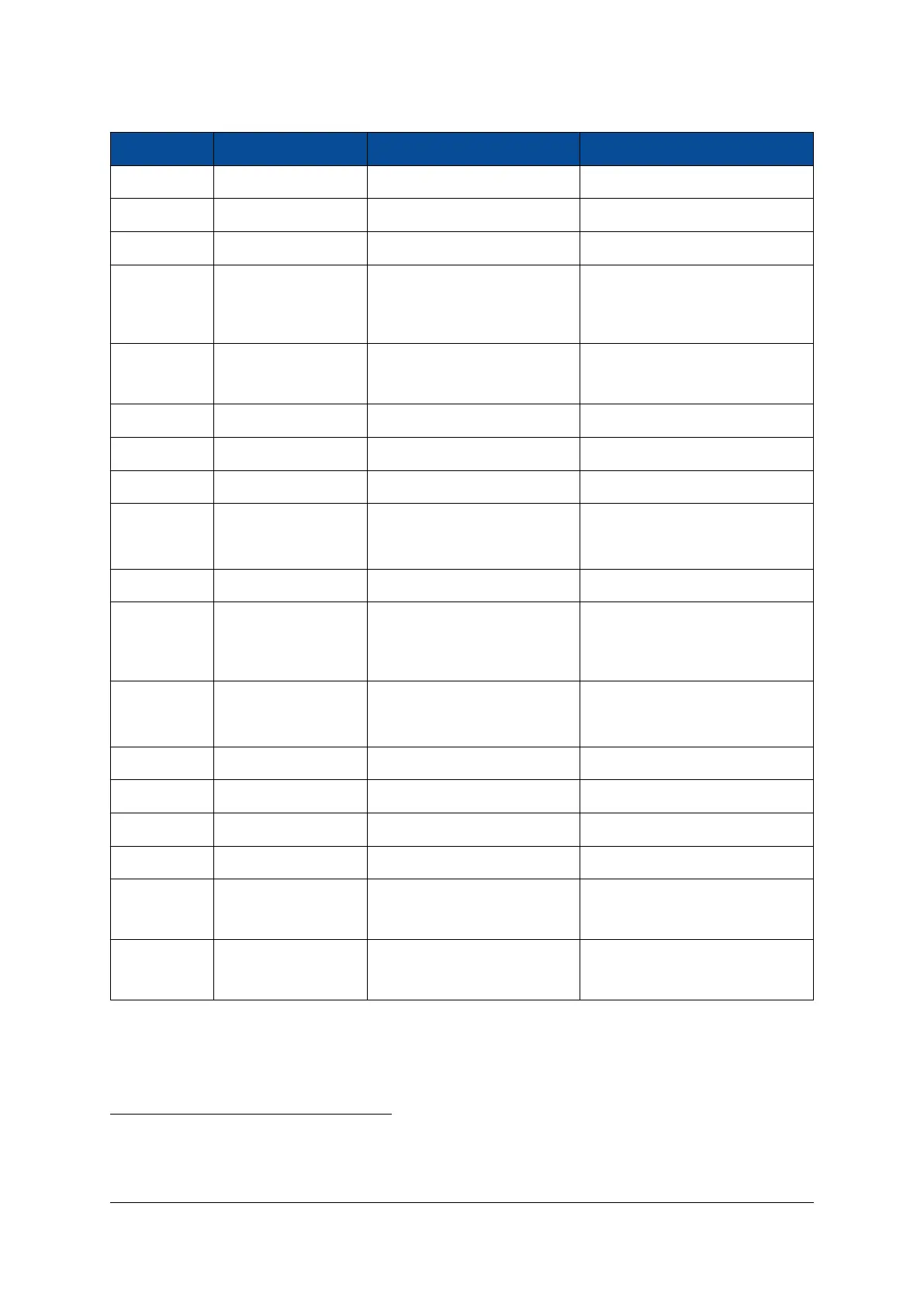

MIO Group Default Function Second Function Connection

0-5 QSPI flash Trace interface QSPI flash, debug connector

6

6 QSPI feedback clock Trace interface (cont.) Debug connector

6

7-9 - Trace interface (cont.) Debug connector

6

10-11 I2C - On-board I2C bus and module

and debug connectors

6

via level

shifter

12 I2C interrupt PJTAG interface On-board I2C bus, debug

connector

6

13-15 eMMC flash PJTAG interface (cont.) eMMC flash, debug connector

6

16-22 eMMC flash (cont.) - eMMC flash

23 USB PHY 1 reset - USB 2.0 PHY 1

24 LED0 Debug UART TX

7

LEDs, debug connector

6

25 LED1 Debug UART RX

7

26-29, 31-37 Ethernet 0 - Gigabit Ethernet PHY 0

30 Ethernet 0 (cont.) PS PCIe block PERST# signal

8

Gigabit Ethernet PHY 0 and

module connector via series re-

sistor

38 UART RX

7

User functionality Module connector

39 UART TX

7

40-41, 43-44 User functionality - Module connector

42 User functionality PS PCIe block PERST# signal

8

Module connector

45-51 SD card User functionality Module connector

52-63 USB 0 - USB 2.0 PHY 0

64-75 Ethernet 1 USB 1 Gigabit Ethernet PHY 1, USB 2.0

PHY 1

76-77 Ethernet MDIO - Gigabit Ethernet PHY 1 and PHY

0 via level shifter

Table 11: MIO Pins Connections Overview

7 8

6

Starting with revision 3, the PJTAG, TRACE, and debug UART interfaces to debug connector are not supported anymore. Please

refer to Section 2.25 for details.

7

UART RX is an MPSoC input; UART TX is an MPSoC output.

8

Used for PCIe PERST# connection implementation. Refer to Section 2.9.2 for details.

D-0000-428-001 27 / 66 Version 13, 15.08.2019

Loading...

Loading...