TLE5012B

SSC Registers

User’s Manual 83 Rev. 1.2, 2018-02

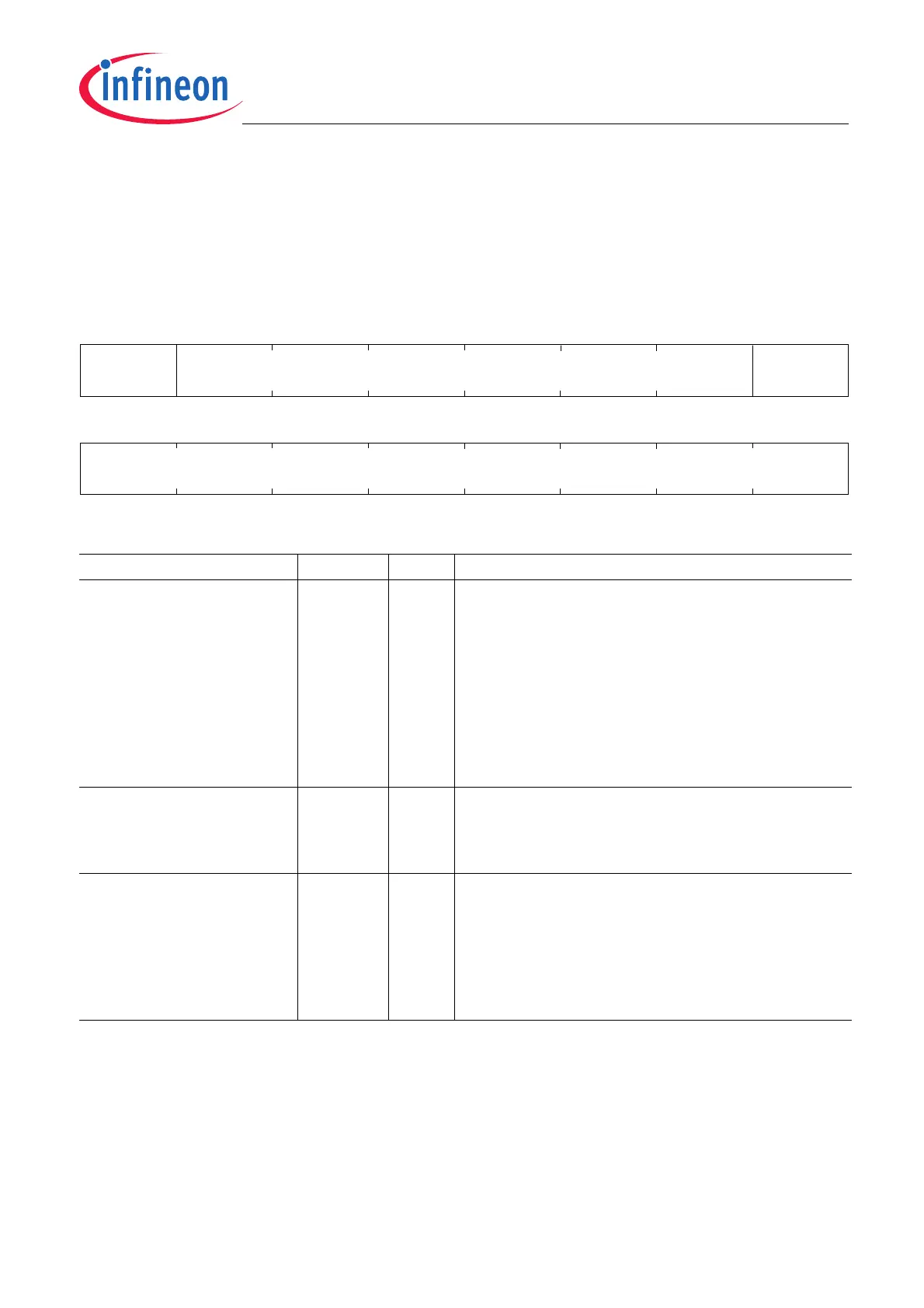

Angle Revolution Register

AREV Offset Reset Value

Angle Revolution Register 04

H

8000

H

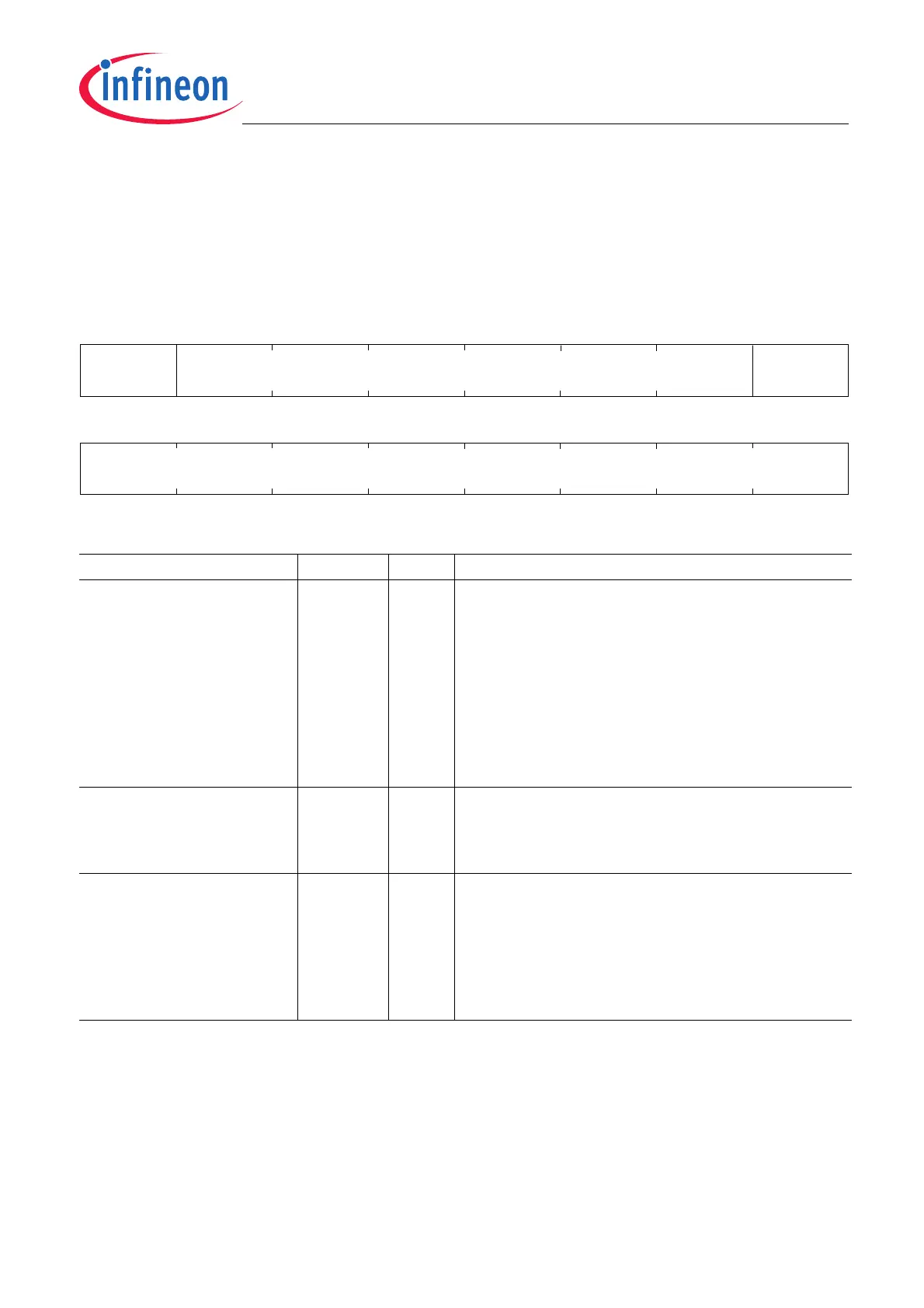

Field Bits Type Description

RD_REV 15 r Read Status, Revolution

0

B

no new values since last readout

1

B

new value (REVOL) present. The bit is cleared on

a read-out (volid for both: normal operation and

update buffer). Note: If an update event (register

snapshot) is done after a normal read, RD_REV will

not be set to 1

B

in the following read (either update

read or normal read) unless a new value is

available.

Reset: 1

B

FCNT 14:9 wu Frame Counter (unsigned 6-bit value)

Internal frame counter. Increments every update period

(FIR_MD setting).

Reset: 0

H

REVOL 8:0 ru Number of Revolutions (signed 9-bit value)

Revolution counter. Increments for every full rotation in

counter-clockwise direction (at angle discontinuity from

360° to 0°) and decrements for every full rotation in

clockwise direction (at angle discontinuity from 0° to

360°). Also see Chapter 4.2.

Reset: 0

H

15 8

7 07 0

RD_REV

14

ru wu

FCNT

REVOL

ru

ru

REVOL

9

Loading...

Loading...