TLE5012B

SSC Registers

User’s Manual 84 Rev. 1.2, 2018-02

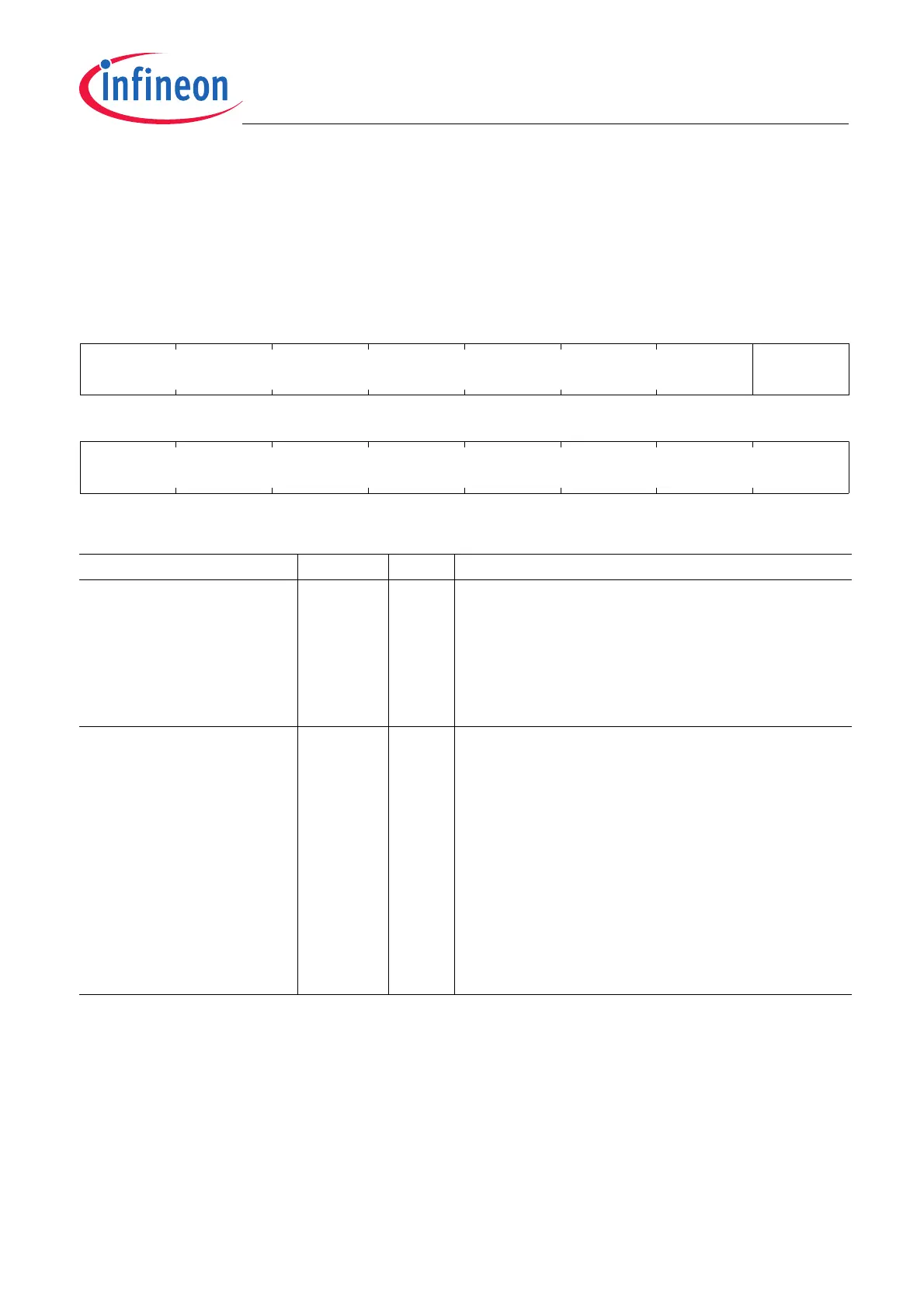

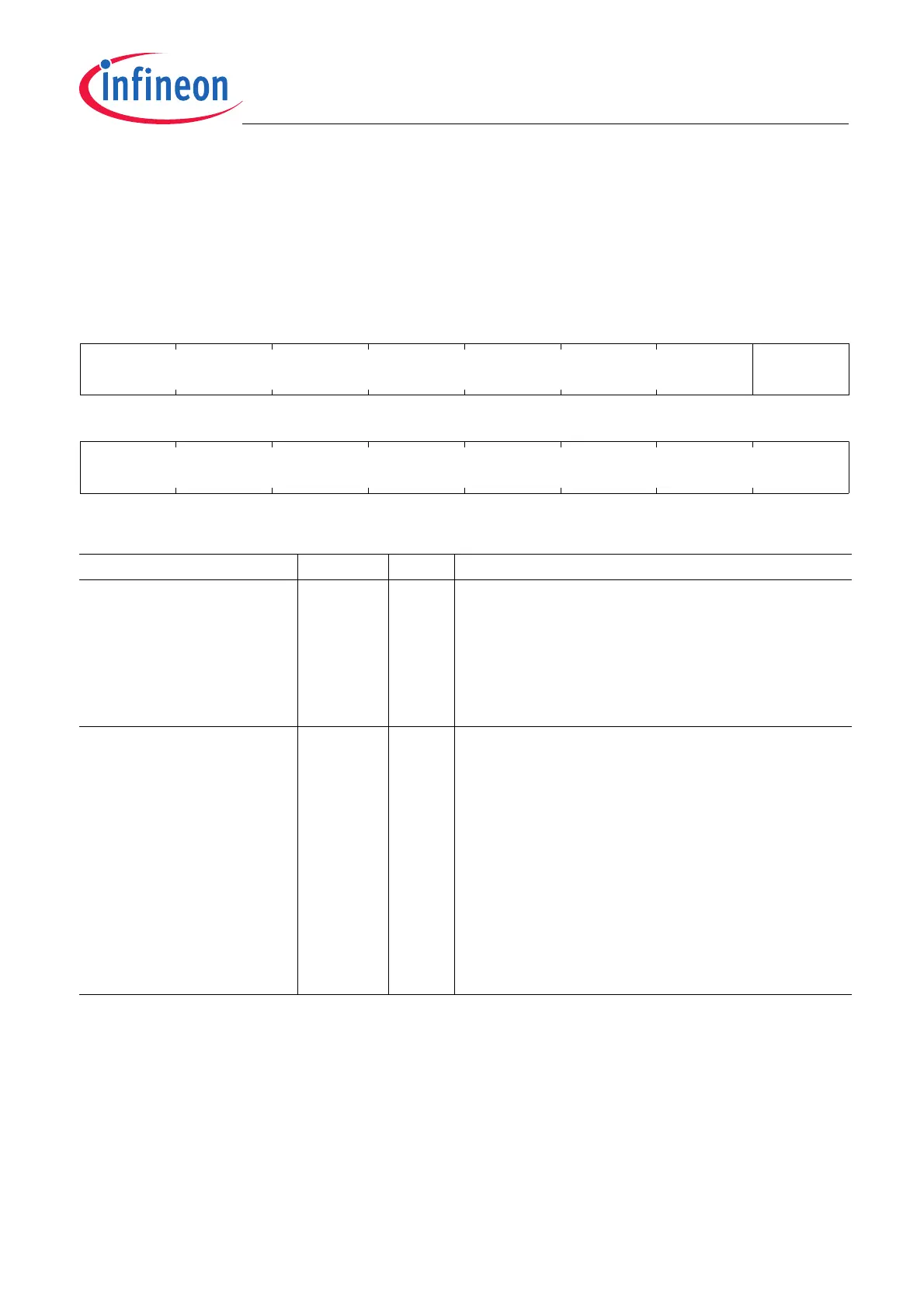

Frame Synchronization Register

FSYNC Offset Reset Value

Frame Synchronization Register 05

H

0000

H

Field Bits Type Description

FSYNC 15:9 wu Frame Synchronization Counter Value

Subcounter within one frame. Increments every internal

clock cycle (synchronously at a 750kHz rate). Maximum

counter value depends on FIR_MD setting: 16 @

FIR_MD=00; 32 @ FIR_MD=01; 64 @ FIR_MD=10; 128

@ FIR_MD=11.

Reset: 0

H

TEMPER 8:0 ru Temperature Value

Signed offset compensated temperature value. Saturated

below approx. -30°C and above approx. +140°C.

Compensation done by DSPU from T_RAW and the

offset temperature T25O.

T[°C] = (TEMPER[dig]+161[dig]) / 2.776[dig/°C]

For reference point on the real temperature the voltage

via the ESD diode at V

DD

pin is used. This introduces

some variation from device to device. After

characterization, a 9-bit correction is considered more

accurate to extract the temperature:

T[°C] = (TEMPER[dig]+152[dig]) / 2.776[dig/°C]

Reset: 0

H

15 8

7 0

15 9

wu

FSYNC

8

ru

TEMPER

7 0

ru

TEMPER

Loading...

Loading...