TLE5012B

SSC Registers

User’s Manual 85 Rev. 1.2, 2018-02

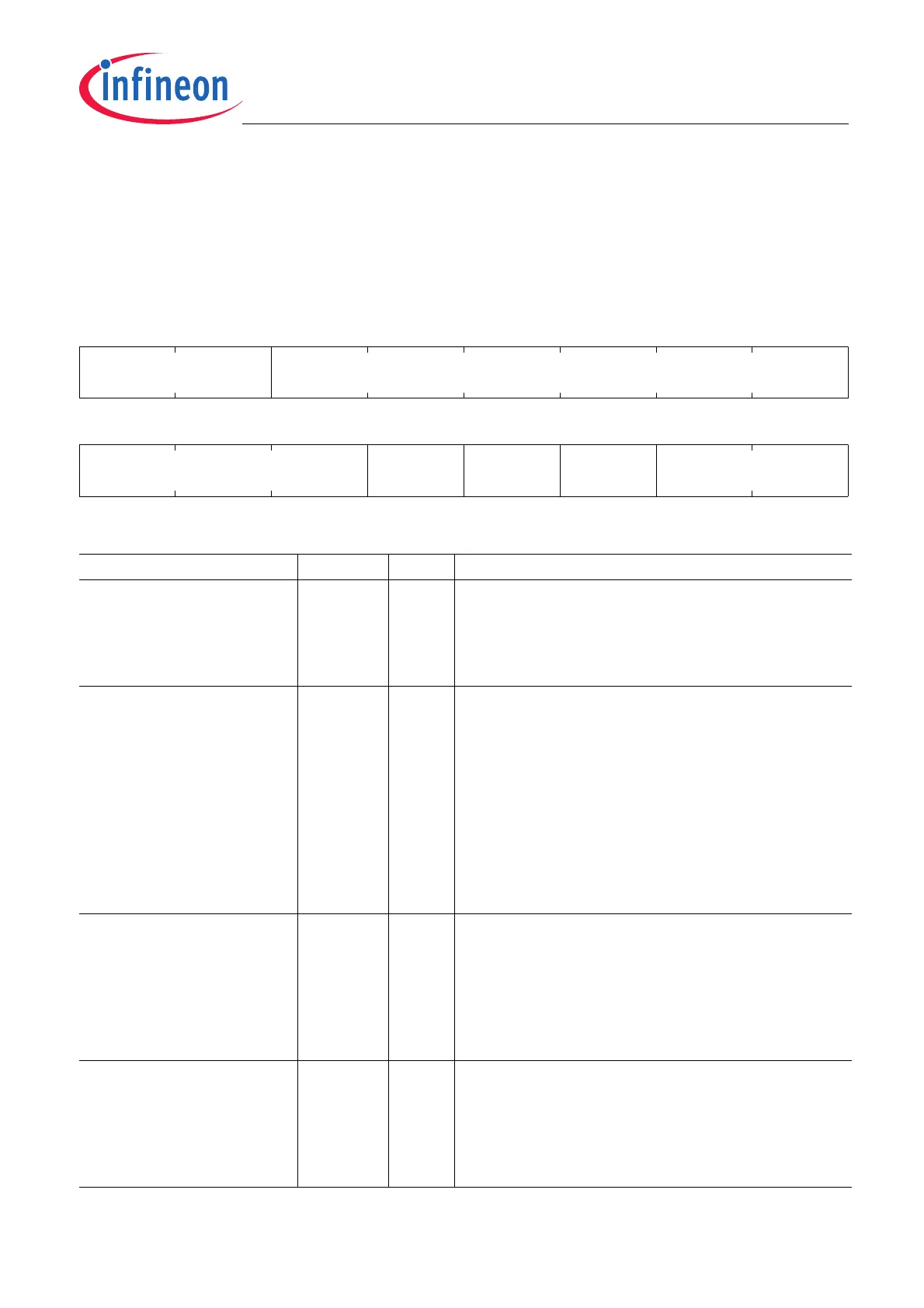

Interface Mode1 Register

MOD_1 Offset Reset Value

Interface Mode1 Register 06

H

derivate-specific

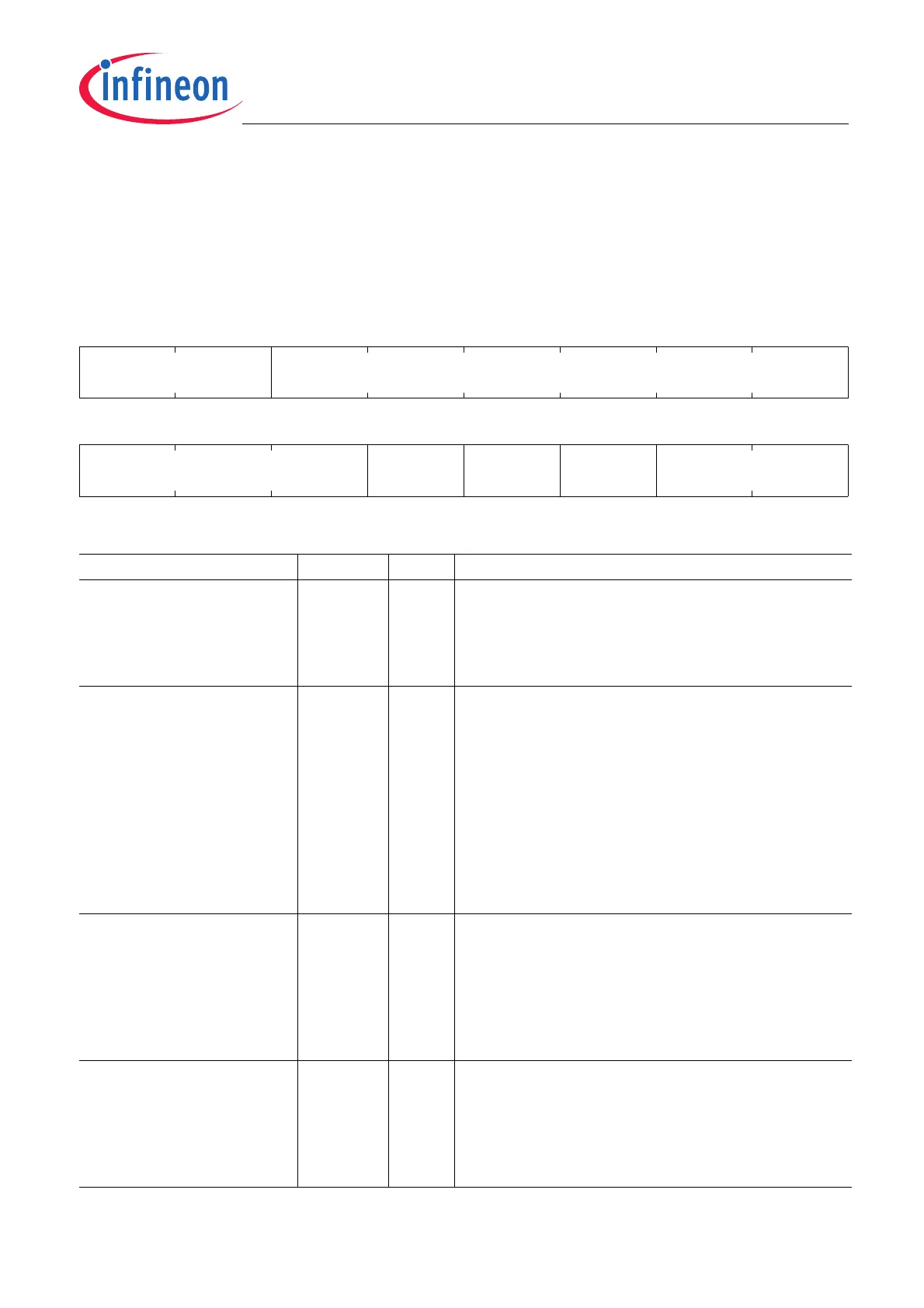

Field Bits Type Description

FIR_MD 15:14 w Update Rate Setting (Filter Decimation)

01

B

42.7 µs

10

B

85.3 µs

11

B

170.6 µs

Reset: derivate-specific

CLK_SEL 4 w Clock Source Select

Switch to external clock at start-up only. If there is no

clock signal on the IFC pin when the chip is switched to

the external clock source, the chip does not allow the

switch (CLK_SEL remains zero, operation continued). If

the external clock disappears with CLK_SEL already set,

the chip will reset (PLL out of lock) and run on with the

internal clock.

0

B

internal oscillator

1

B

external 4-MHz clock (IFC pin switched to input)

Reset: 0

B

DSPU_HOLD 2 w Hold DSPU Operation

1)

If DSPU is on hold, no watchdog reset is performed by

DSPU. Deactivate watchdog with AS_WD before setting

DSPU on hold.

0

B

DSPU in normal schedule operation

1

B

DSPU is on hold

Reset: 0

B

1) DSPU_HOLD is ignored in PWM or SPC mode.

IIF_MOD 1:0 w Incremental Interface Mode

00

B

IIF disabled

01

B

A/B operation with Index on IFC pin

10

B

Step/Direction operation with Index on IFC pin

11

B

not allowed

Reset: derivate-specific

15 8

7 0

15 14

w

FIR_MD

13

Res

75

Res

44

w

CLK_SEL

33

Res

22

w

DSPU_HO

LD

10

w

IIF_MOD

Loading...

Loading...