6482-901-01 Rev. A / August 2012 Return to Section Topics 16-31

Model 6482 Dual-Channel Picoammeter / Voltage Source Reference Manual Section 16: SCPI Command Reference

Bit 8 (LIMIT_A): Encoded limit test summary bit. See grading and sorting modes

in “Limit test bits” below.

Bit 9 (LIMIT_B): Encoded limit test summary bit. See below.

Bit 10 (LIMIT_C): Encoded limit test summary bit. See below.

Bit 11 (LIMIT_D): Encoded limit test summary bit. See below.

Bit 12 (LIMIT_HIGH): Limit test 3 - 6 failed high. See below.

Bit 13 (CH1_OUTPUT): Set to 1 if the channel 1 source output is on. Cleared to 0

otherwise.

Bit 14 (CH2_OUTPUT): Set to 1 if the channel 2 source output is on. Cleared to 0

otherwise.

Bit 15: Not used.

Limit test bits Bits 8 through 12 flag pass/fail conditions for the various limit tests. The bit values

for the grading and sorting modes are covered below. See :CALC7:CLIM:MODE

and associated commands in “Calculate subsystems,” page Section 16-16.

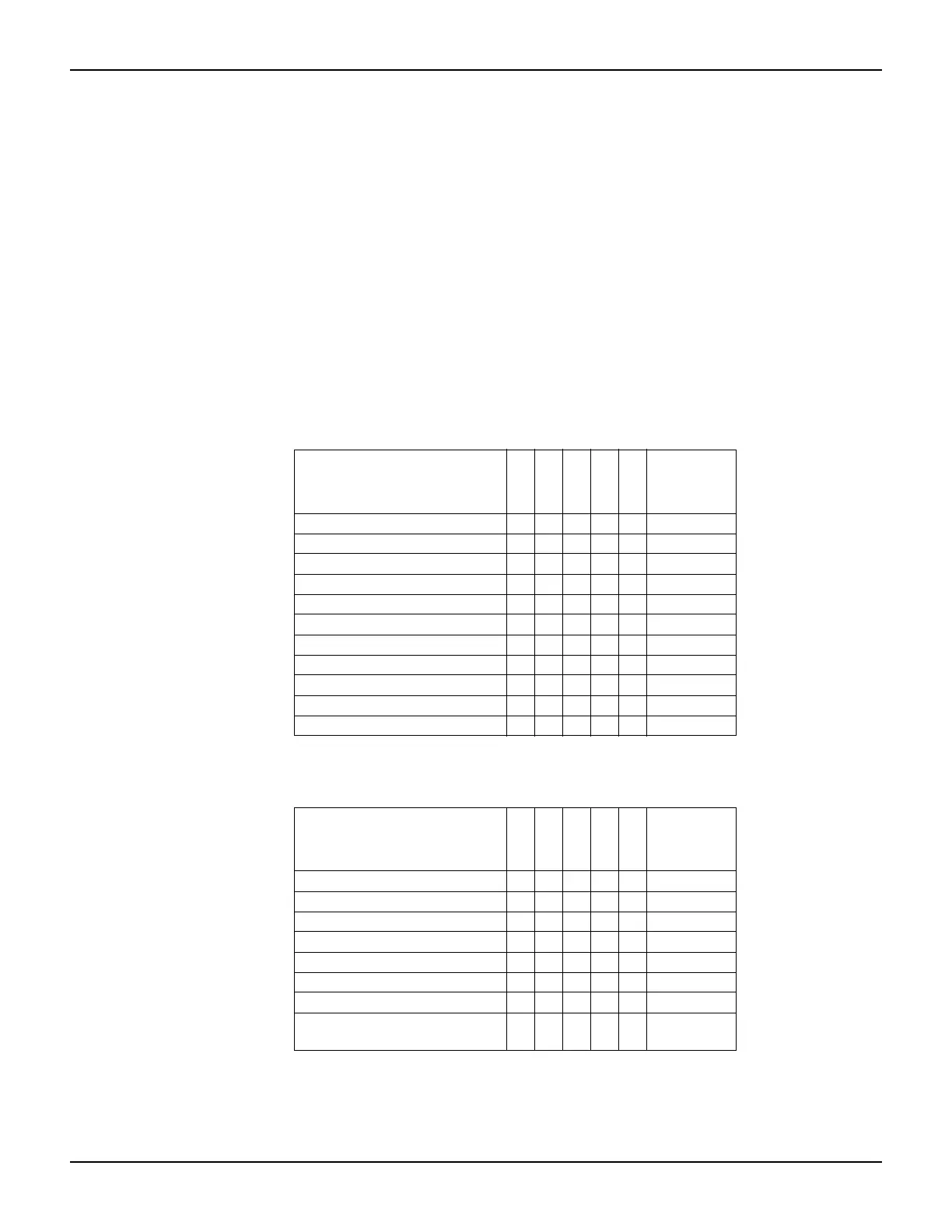

Grading mode status bit values:

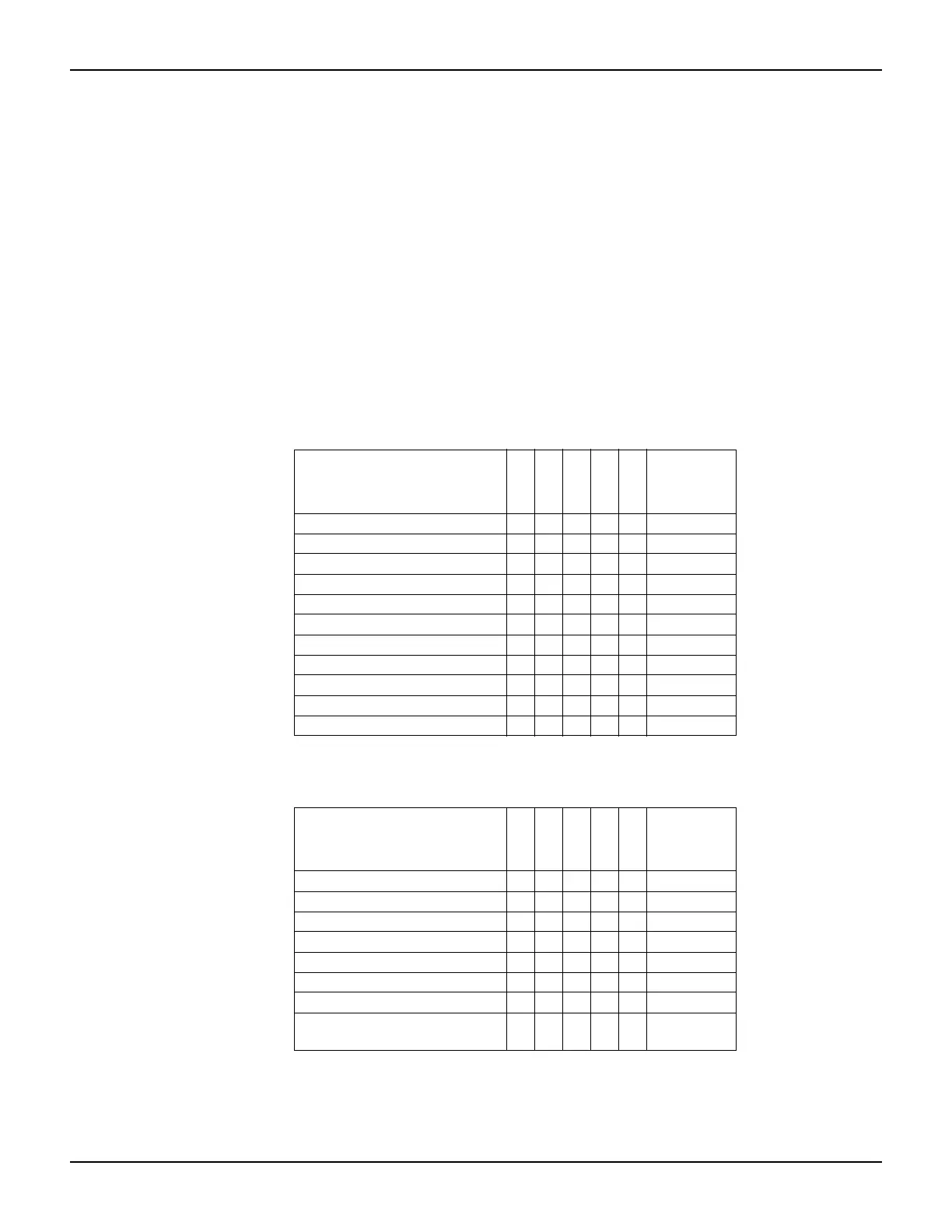

Sorting mode status bit values:

Result Bit #: 12 11 10 9 8

Meas.

Event

Status

1

All limit tests passed 0 0 0 0 0 Bit 5 (LP)

Limit test 1 failed 0 0 0 0 1 Bit 0 (L1)

Limit test 2 failed 0 0 0 1 0 Bit 1 (L2)

Limit test 3 high failed 1 0 0 1 1 Bit 4 (LFH)

Limit test 3 low failed 0 0 0 1 1 Bit 2 (L3)

Limit test 4 high failed 1 0 1 0 0 Bit 4 (LFH)

Limit test 4 low failed 0 0 1 0 0 Bit 3 (L4)

Limit test 5 high failed 1 0 1 0 1 -

Limit test 5 low failed 0 0 1 0 1 -

Limit test 6 high failed 1 0 1 1 0 Bit 4 (LFH)

Limit test 6 low failed 0 0 1 1 0 -

1

See Section 13, “Measurement event register,” and Figure 13-6 for details.

Result Bit #: 12 11 10 9 8

Meas.

Event

Status

1

Limit 1 & 2 passed, 3-6 disabled 0 0 0 0 0 Bit 5 (LP)

Limit test 1 failed 0 0 0 0 1 Bit 0 (L1)

Limit test 2 failed 0 0 0 1 0 Bit 1 (L2)

Limit test 3 passed 0 0 0 1 1 Bit 3 (L3)

Limit test 4 passed 0 0 1 0 0 Bit 4 (L4)

Limit test 5 passed 0 0 1 0 1 -

Limit test 6 passed 0 0 1 1 0 -

All Limits 3 - 6 failed,

Limits 1 and 2 passed

1 1 1 1 1 -

1

See Section 13, “Measurement event register,” and Figure 13-6 for details.

Loading...

Loading...