Circuit Descriptions, Abbreviation List, and IC Data Sheets

EN 140 Q528.1E LA9.

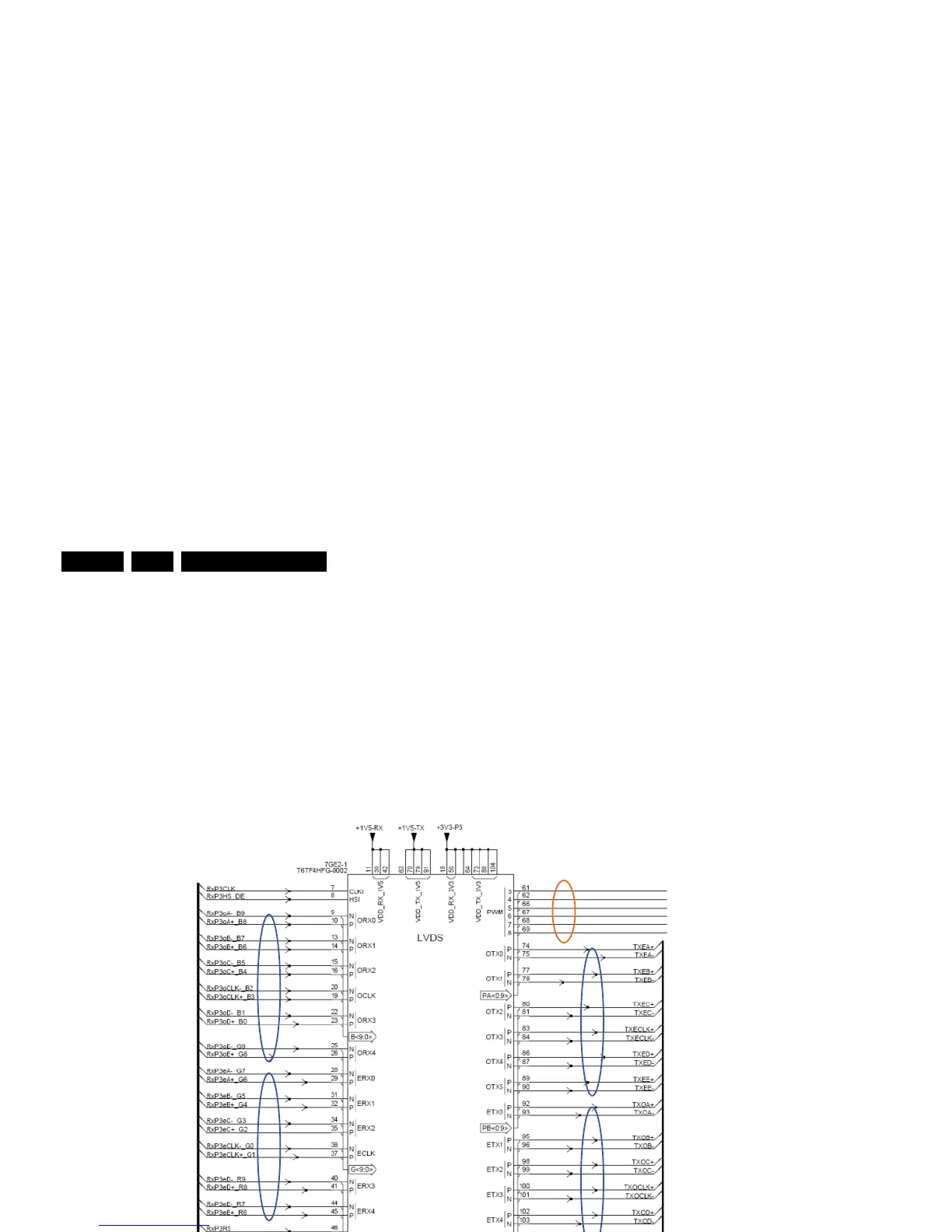

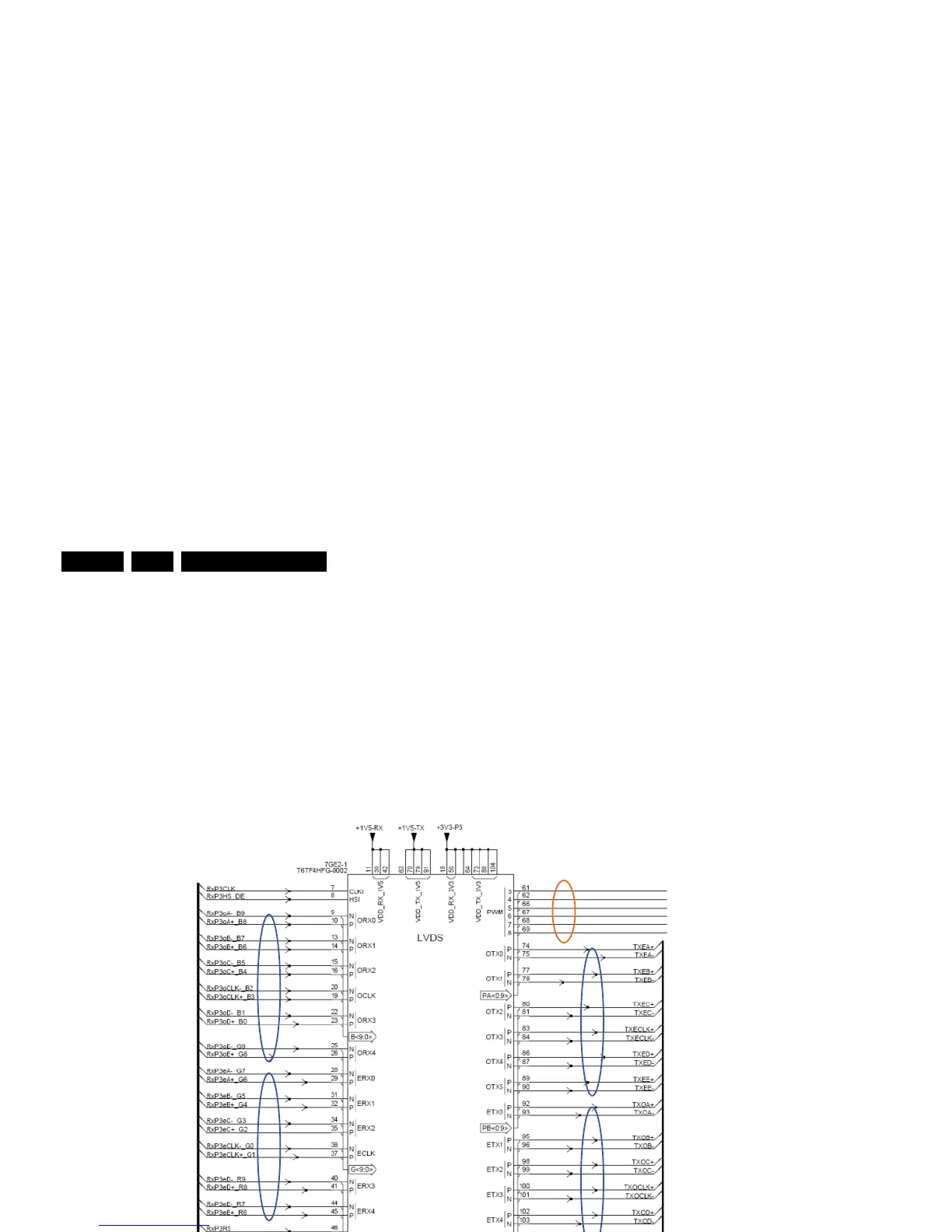

9.7.5 PACIFIC 3 (T6TF4HFG)

The PACIFIC 3 performs the following tasks:

• Colour processing.

• Sharpness improvement.

• Backlight dimming.

• AmbiLight.

• Display (LVDS) switch on/off.

• Pattern generator.

The PACIFIC 3 interfaces:

• Video input:

– US sets: single LVDS from PNX8535, dual LVDS from

CYCLONE II

– CMOS from PNX5050

• Video output: LVDS (single or dual) to display or DFI panel.

• Backlight dimming: pulse-width modulated (PWM) followed

by PWM to I

2

C conversion.

• AmbiLight: pulse-width modulated (PWM) followed by

microprocessor.

Refer to figure “PACIFIC 3 CMOS + LVDS interface” for details.

Figure 9-18 PACIFIC 3 CMOS + LVDS interface

A configuration flash memory is added (item 7GE1).

Pacific CMOS/LVDS input & LVDS output

Single LVDS

-

in

(

PNX8535)

Double LVDS in

(

FPGA

)

Single or double

LVDS

-out to display

PW M am bi

to µP

H_16770_137a.eps

290307

Loading...

Loading...