R8C/1A Group, R8C/1B Group 14. Timers

Rev.1.30 Dec 08, 2006 Page 150 of 315

REJ09B0252-0130

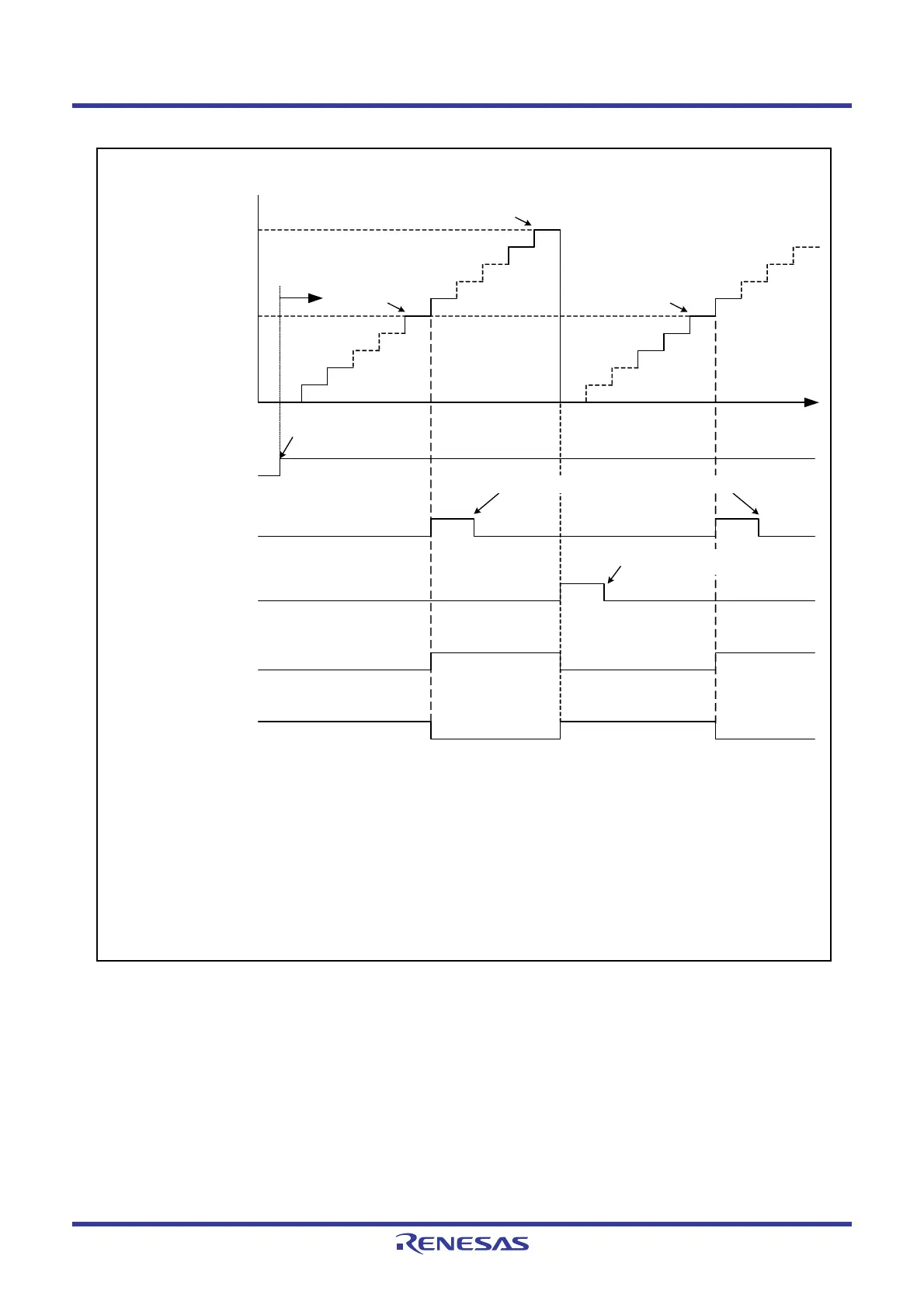

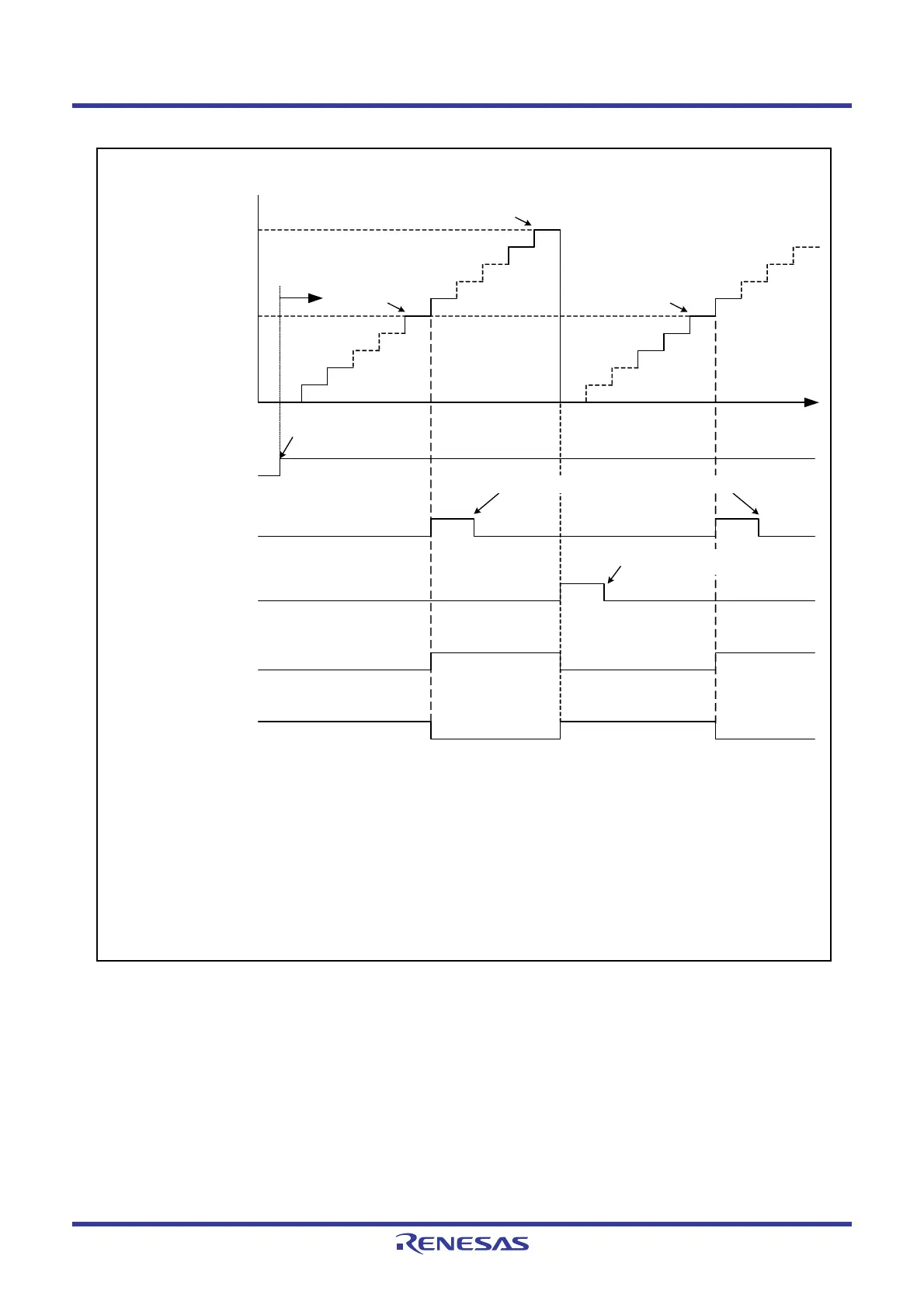

Figure 14.31 Operating Example in Output Compare Mode

Value set in TM1 register

0000h

Counter content (hex)

Count starts

Match

Time

TCC00 bit in

TCC0 register

1

0

IR bit in CMP0IC

register

1

0

TCC12 bit in TCC1 register = 1 (TC register is set to 0000h at compare 1 match occurrence )

TCC13 bit in TCC1 register = 1 (Compare 0 output selected)

TCC15 to TCC14 bits in TCC1 register = 11b (CMP output level is set to high at compare 0 match occurrence)

TCC17 to TCC16 bits in TCC1 register = 10b (CMP output level is set to low at compare 1 match occurrence)

TCOUT6 bit in TCOUT register = 0 (not inverted)

TCOUT7 bit in TCOUT register = 1 (inverted)

TCOUT0 bit in TCOUT register = 1 (CMP0_0 output enabled)

TCOUT3 bit in TCOUT register = 1 (CMP1_0 output enabled)

P1_0 bit in P1 register = 1 (high)

P3_0 bit in P3 register = 1 (high)

Set to 1 by program

IR bit in CMP1IC

register

1

0

Value set in TM0 register

Match Match

CMP0_0 output

1

0

1

0

CMP1_0 output

Set to 0 when interrupt request is acknowledged, or set by program

Set to 0 when interrupt request is

acknowledged, or set by program

The above applies to the following conditions :

Loading...

Loading...