R8C/1A Group, R8C/1B Group 12. Interrupts

Rev.1.30 Dec 08, 2006 Page 98 of 315

REJ09B0252-0130

12.4 Address Match Interrupt

An address match interrupt request is generated immediately before execution of the instruction at the address

indicated by the RMADi register (i = 0, 1). This interrupt is used as a break function by the debugger. When using

the on-chip debugger, do not set an address match interrupt (registers of AIER, RMAD0, and RMAD1 and fixed

vector tables) in a user system.

Set the starting address of any instruction in the RMADi register. Bits AIER0 and AIER1 in the AIER0 register can

be used to select enable or disable of the interrupt. The I flag and IPL do not affect the address match interrupt.

The value of the PC (Refer to 12.1.6.7 Saving a Register for the value of the PC) which is saved to the stack when

an address match interrupt is acknowledged varies depending on the instruction at the address indicated by the

RMADi register. (The appropriate return address is not saved on the stack.) When returning from the address match

interrupt, return by one of the following means:

• Change the content of the stack and use the REIT instruction.

• Use an instruction such as POP to restore the stack as it was before the interrupt request was acknowledged.

Then use a jump instruction.

Table 12.6 lists the Values of PC Saved to Stack when Address Match Interrupt is Acknowledged.

Figure 12.19 shows Registers AIER, and RMAD0 to RMAD1.

NOTES:

1. Refer to the 12.1.6.7 Saving a Register for the PC value saved.

2. Operation code: Refer for the “R8C/Tiny Series Software Manual (REJ09B0001)”.

“Chapter 4. Instruction Code/Number of Cycles” contains diagrams showing

operation code below each syntax. Operation code is shown in the bold frame in

the diagrams.

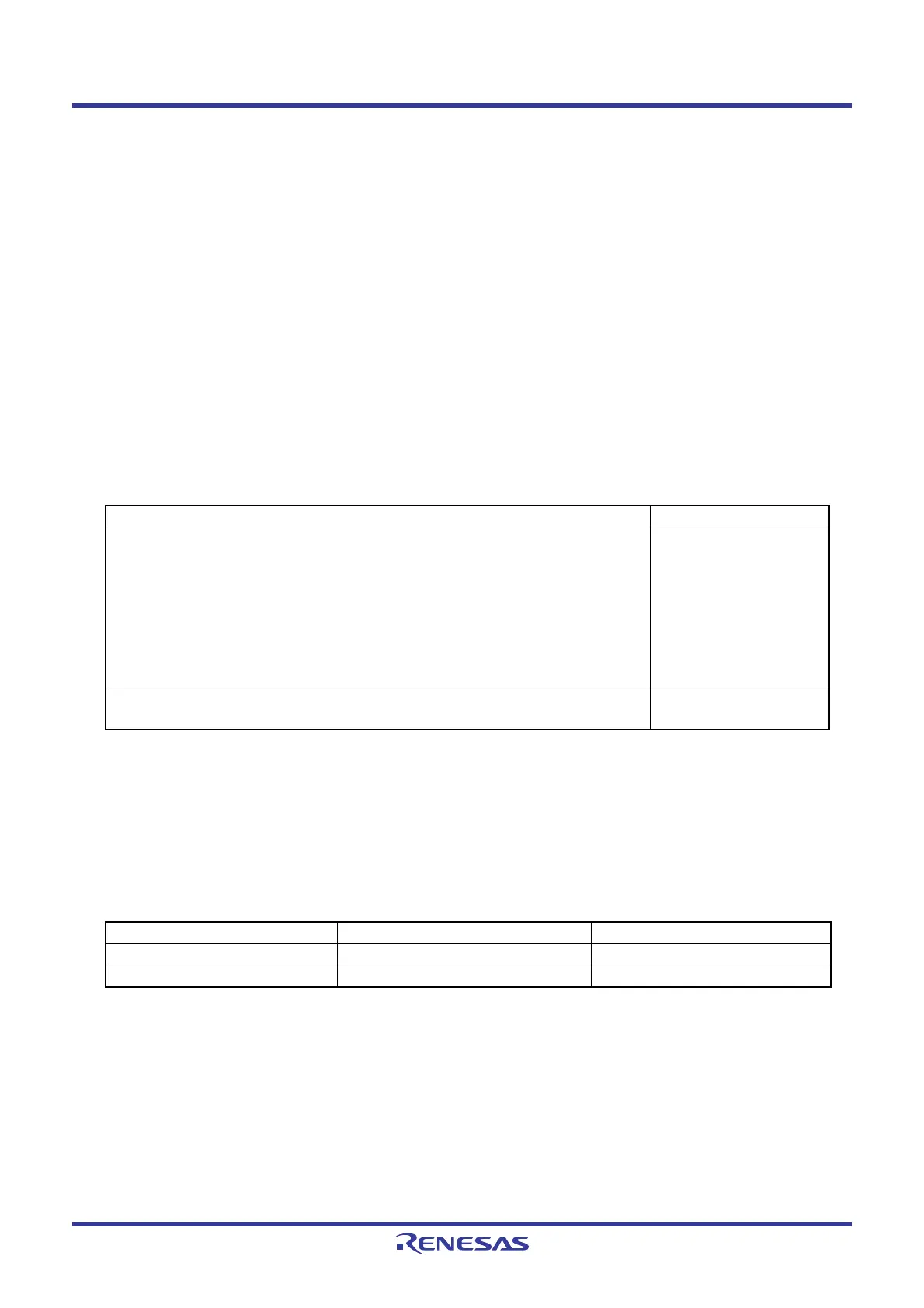

Table 12.6 Values of PC Saved to Stack when Address Match Interrupt is Acknowledged

Address Indicated by RMADi Register (i = 0,1) PC Value Saved

(1)

• Instruction with 2-byte operation code

(2)

• Instruction shown below among instruction with 1-byte operation code

(2)

ADD.B:S #IMM8,dest SUB.B:S #IMM8,dest AND.B:S #IMM8,dest

OR.B:S #IMM8,dest MOV.B:S #IMM8,dest STZ.B:S #IMM8,dest

STNZ.B:S #IMM8,dest STZX.B:S #IMM81,#IMM82,dest

CMP.B:S #IMM8,dest PUSHM src POPM dest

JMPS #IMM8 JSRS #IMM8

MOV.B:S #IMM,dest (however, dest = A0 or A1)

Address indicated by

RMADi register + 2

• Instructions other than the above Address indicated by

RMADi register + 1

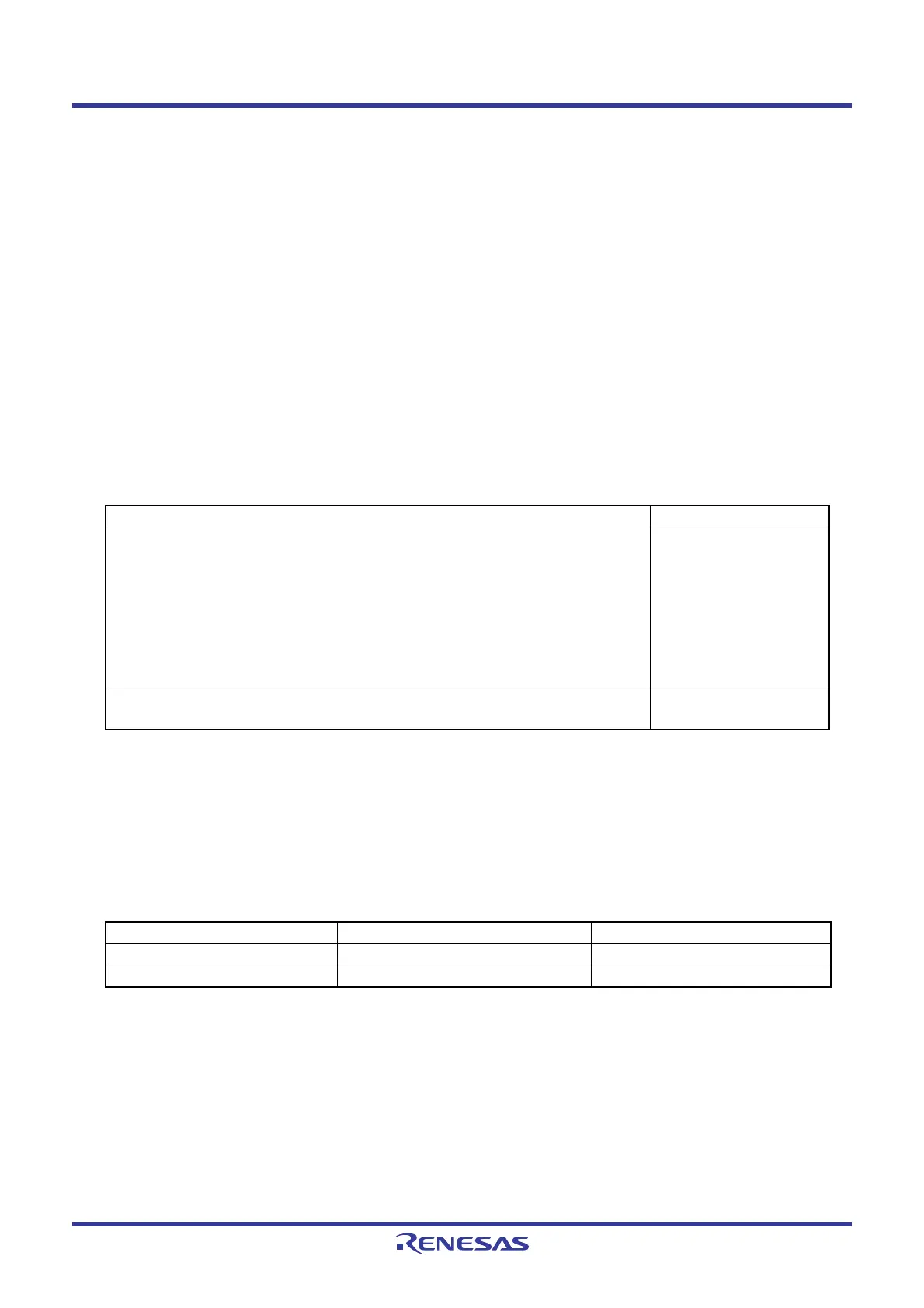

Table 12.7 Correspondence Between Address Match Interrupt Sources and Associated

Registers

Address Match Interrupt Source Address Match Interrupt Enable Bit Address Match Interrupt Register

Address match interrupt 0 AIER0 RMAD0

Address match interrupt 1 AIER1 RMAD1

Loading...

Loading...