R8C/1A Group, R8C/1B Group 16. Clock Synchronous Serial Interface

Rev.1.30 Dec 08, 2006 Page 182 of 315

REJ09B0252-0130

16.2.3 Interrupt Requests

Clock synchronous serial I/O with chip select has five interrupt requests: transmit data empty, transmit end,

receive data full, overrun error, and conflict error. Since these interrupt requests are assigned to the clock

synchronous serial I/O with chip select interrupt vector table, determining interrupt sources by flags is required.

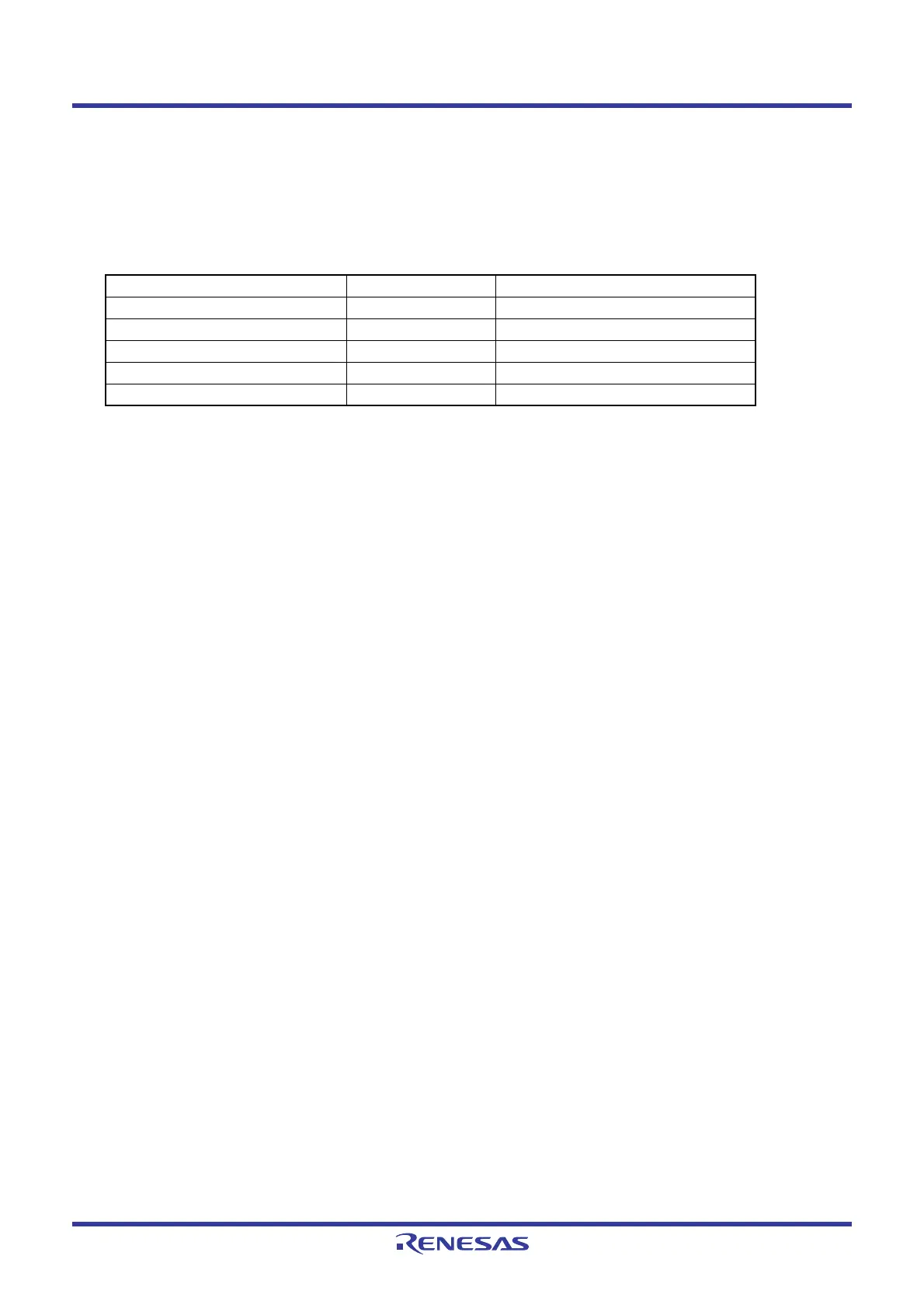

Table 16.3 shows the Clock Synchronous Serial I/O with Chip Select Interrupt Requests.

CEIE, RIE, TEIE, and TIE: Bits in SSER register

ORER, RDRF, TEND, and TDRE: Bits in SSSR register

If the generation conditions in Table 16.3 are met, a clock synchronous serial I/O with chip select interrupt request

is generated. Set each interrupt source to 0 by a clock synchronous serial I/O with chip select interrupt routine.

However, the TDRE and TEND bits are automatically set to 0 by writing transmit data to the SSTDR register and

the RDRF bit is automatically set to 0 by reading the SSRDR register. In particular, the TDRE bit is set to 1 (data

transmitted from registers SSTDR to SSTRSR) at the same time transmit data is written to the SSTDR register.

Setting the TDRE bit to 0 (data not transmitted from registers SSTDR to SSTRSR) can cause an additional byte of

data to be transmitted.

Table 16.3 Clock Synchronous Serial I/O with Chip Select Interrupt Requests

Interrupt Request Abbreviation Generation Condition

Transmit data empty TXI TIE = 1, TDRE = 1

Transmit end TEI TEIE = 1, TEND = 1

Receive data full RXI RIE = 1, RDRF = 1

Overrun error OEI RIE = 1, ORER = 1

Conflict error CEI CEIE = 1, CE = 1

Loading...

Loading...