R8C/1A Group, R8C/1B Group 5. Programmable I/O Ports

Rev.1.30 Dec 08, 2006 Page 32 of 315

REJ09B0252-0130

5.4 Port Settings

Tables 5.4 to 5.17 list the port settings.

X: 0 or 1

X: 0 or 1

X: 0 or 1

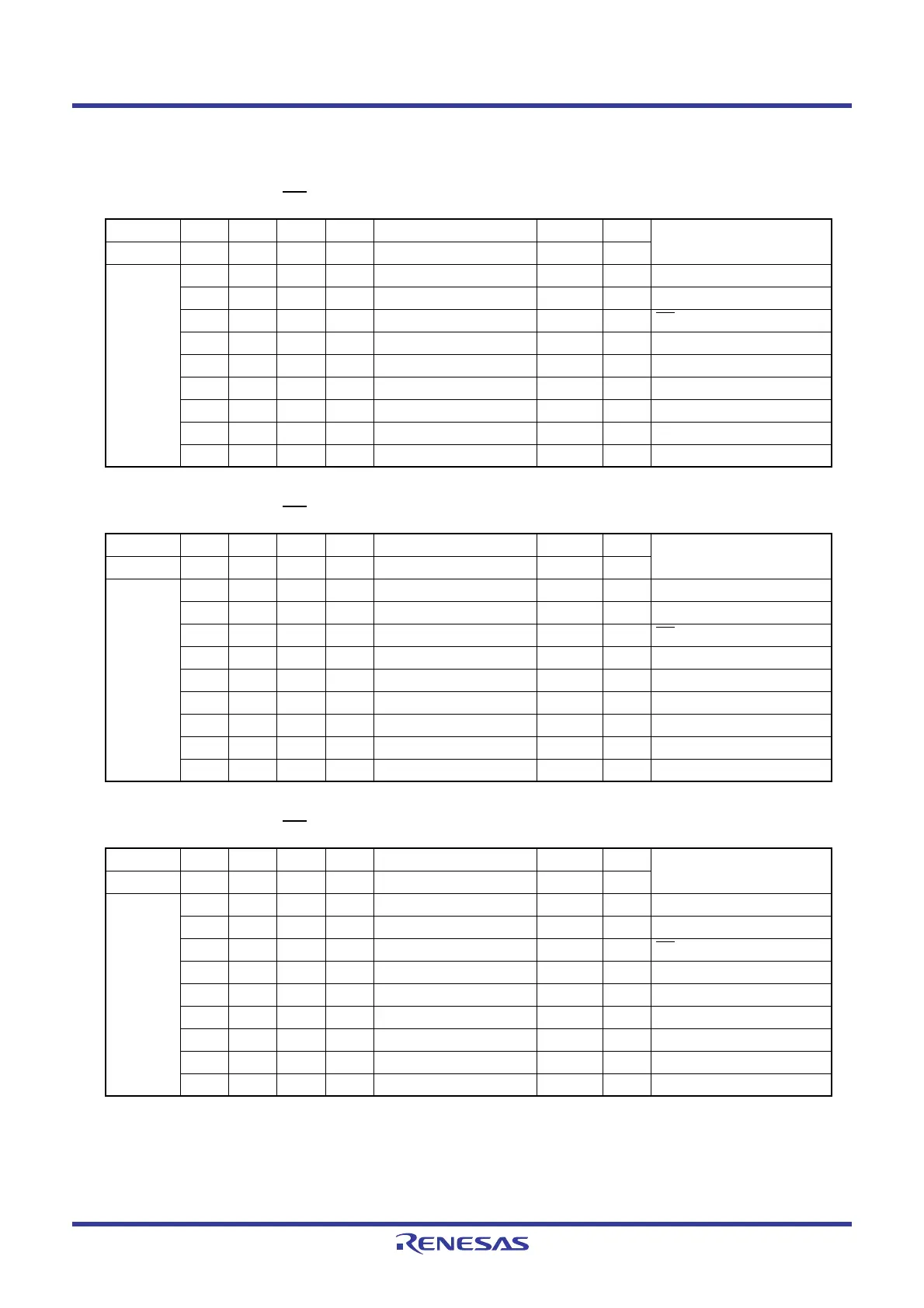

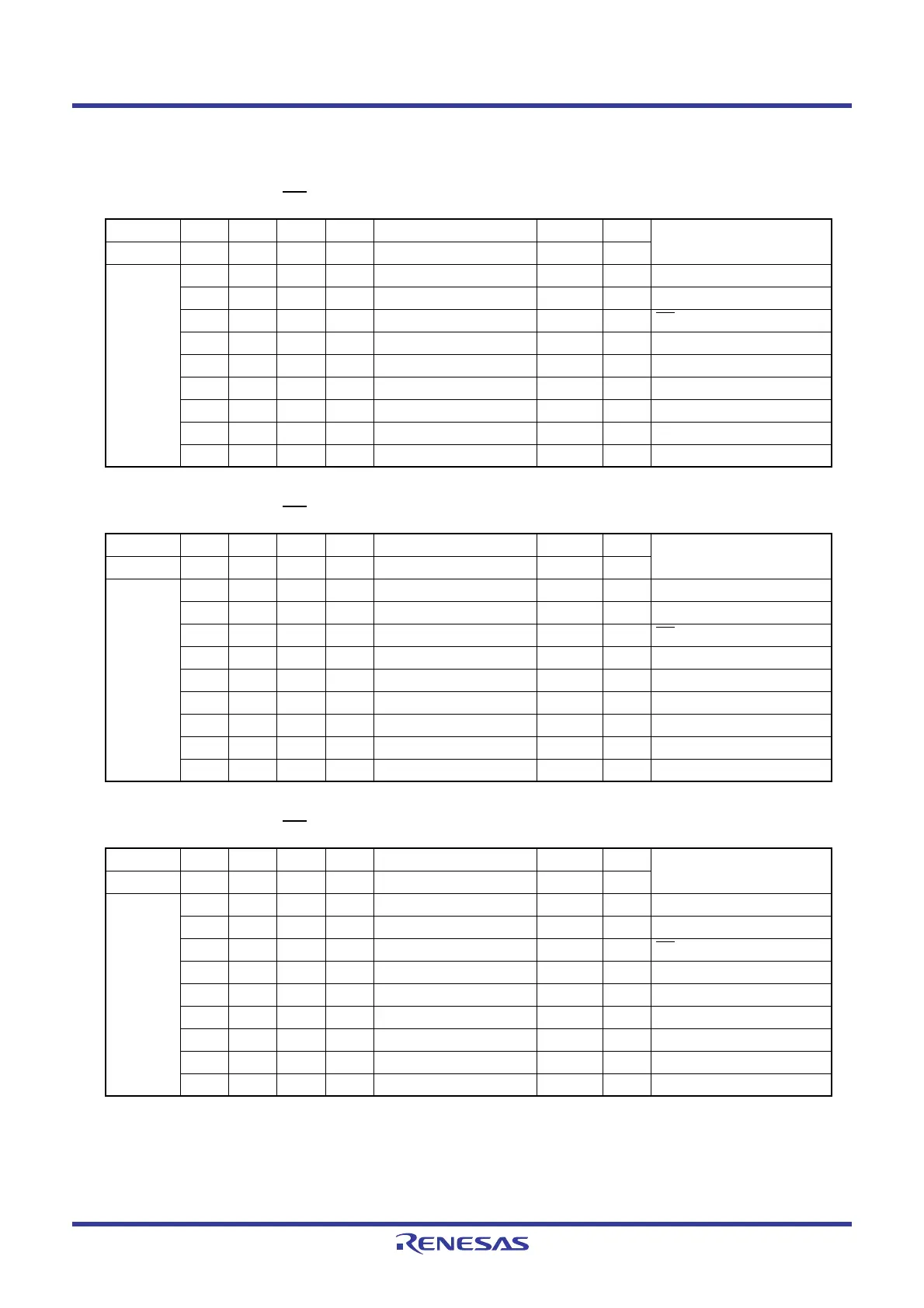

Table 5.4 Port P1_0/KI0/AN8/CMP0_0

Register PD1 PUR0 DRR KIEN ADCON0 TCOUT P1

Function

Bit PD1_0 PU02 DRR0 KI0EN CH2, CH1, CH0, ADGSEL0 TCOUT0 P1_0

Setting

Value

0 0 X X XXXXb 0 X Input port (not pulled up)

0 1 X X XXXXb 0 X Input port (pulled up)

0 0 X 1 XXXXb 0 X KI0

input

0 0 X X 1001b 0 X A/D Converter input (AN8)

1 X 0 X XXXXb 0 X Output port

1 X 1 X XXXXb 0 X Output port (High drive)

X X 0 X XXXXb 1 0 Output port

X X 1 X XXXXb 1 0 Output port (High drive)

X X X X XXXXb 1 1 CMP0_0 output

Table 5.5 Port P1_1/KI1/AN9/CMP0_1

Register PD1 PUR0 DRR KIEN ADCON0 TCOUT P1

Function

Bit PD1_1 PU02 DRR1 KI1EN CH2, CH1, CH0, ADGSEL0 TCOUT1 P1_1

Setting

Value

0 0 X X XXXXb 0 X Input port (not pulled up)

0 1 X X XXXXb 0 X Input port (pulled up)

0 0 X 1 XXXXb 0 X KI1

input

0 0 X X 1011b 0 X A/D converter input (AN9)

1 X 0 X XXXXb 0 X Output port

1 X 1 X XXXXb 0 X Output port (high drive)

X X 0 X XXXXb 1 0 Output port

X X 1 X XXXXb 1 0 Output port (high drive)

X X X X XXXXb 1 1 CMP0_1 output

Table 5.6 Port P1_2/KI2/AN10/CMP0_2

Register PD1 PUR0 DRR KIEN ADCON0 TCOUT P1

Function

Bit PD1_2 PU02 DRR2 KI2EN CH2, CH1, CH0, ADGSEL0 TCOUT2 P1_2

Setting

Value

0 0 X X XXXXb 0 X Input port (not pulled up)

0 1 X X XXXXb 0 X Input port (pulled up)

0 0 X 1 XXXXb 0 X KI2

input

0 0 X X 1101b 0 X A/D converter input (AN10)

1 X 0 X XXXXb 0 X Output port

1 X 1 X XXXXb 0 X Output port (high drive)

X X 0 X XXXXb 1 0 Output port

X X 1 X XXXXb 1 0 Output port (high drive)

X X X X XXXXb 1 1 CMP0_2 input

Loading...

Loading...