R8C/1A Group, R8C/1B Group 17. A/D Converter

Rev.1.30 Dec 08, 2006 Page 232 of 315

REJ09B0252-0130

17. A/D Converter

The A/D converter consists of one 10-bit successive approximation A/D converter circuit with a capacitive coupling

amplifier. The analog input shares pins P1_0

to P1_3. Therefore, when using these pins, ensure that the corresponding

port direction bits are set to 0 (input mode).

When not using the A/D converter, set the VCUT bit in the ADCON1 register to 0 (Vref unconnected) so that no

current will flow from the VREF

pin into the resistor ladder. This helps to reduce the power consumption of the chip.

The result of A/D conversion is stored in the AD register.

Table 17.1 lists the Performance of A/D Converter. Figure 17.1 shows a Block Diagram of A/D Converter.

Figures 17.2 and 17.3 show the A/D Converter-Associated Registers.

NOTES:

1. The analog input voltage does not depend on use of a sample and hold function.

When the analog input voltage is over the reference voltage, the A/D conversion result will be 3FFh

in 10-bit mode and FFh in 8-bit mode.

2. The frequency of φAD must be 10 MHz or below.

Without a sample and hold function, the φAD frequency should be 250 kHz or above.

With a sample and hold function, the φAD frequency should be 1 MHz or above.

3. In repeat mode, only 8-bit mode can be used.

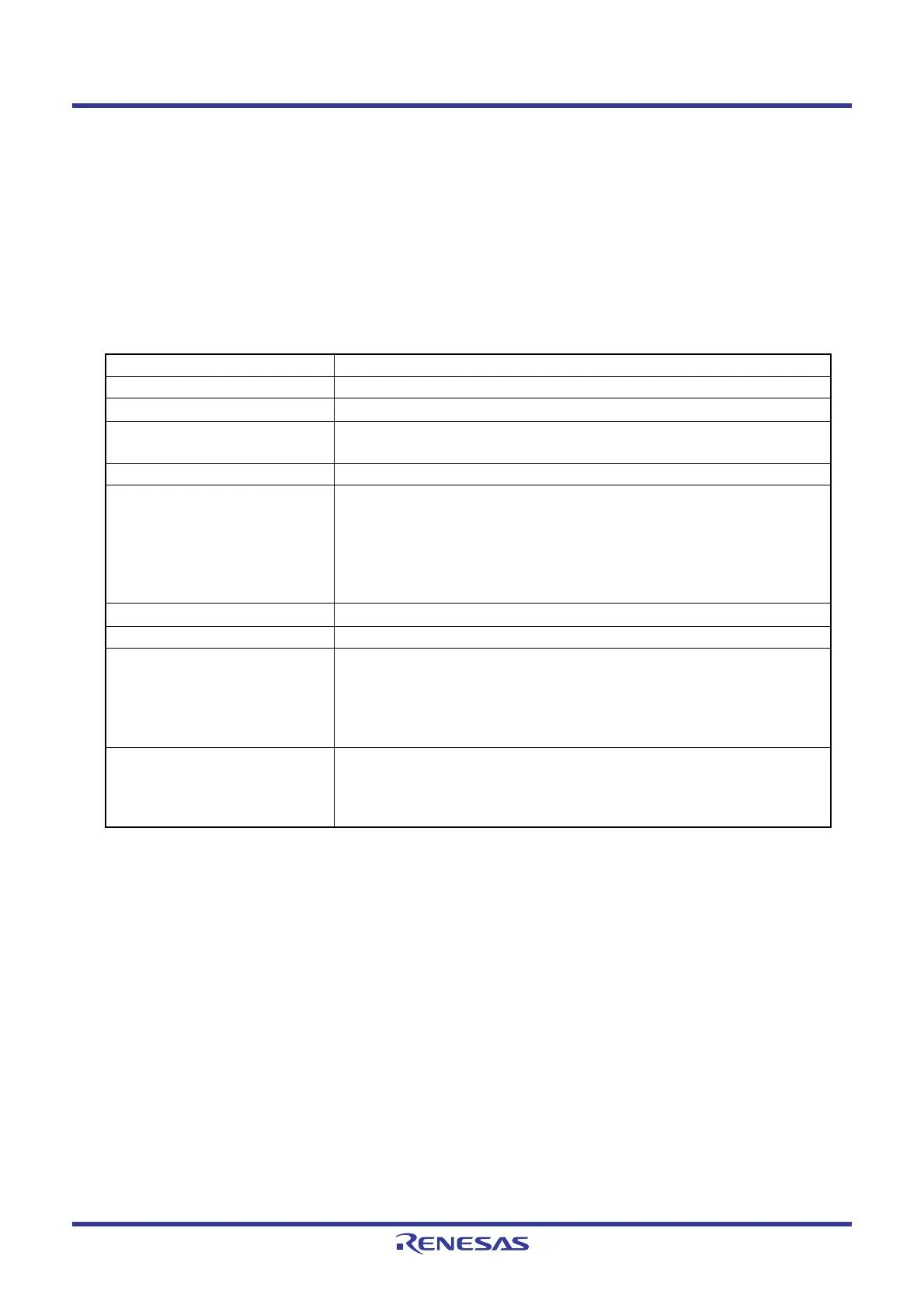

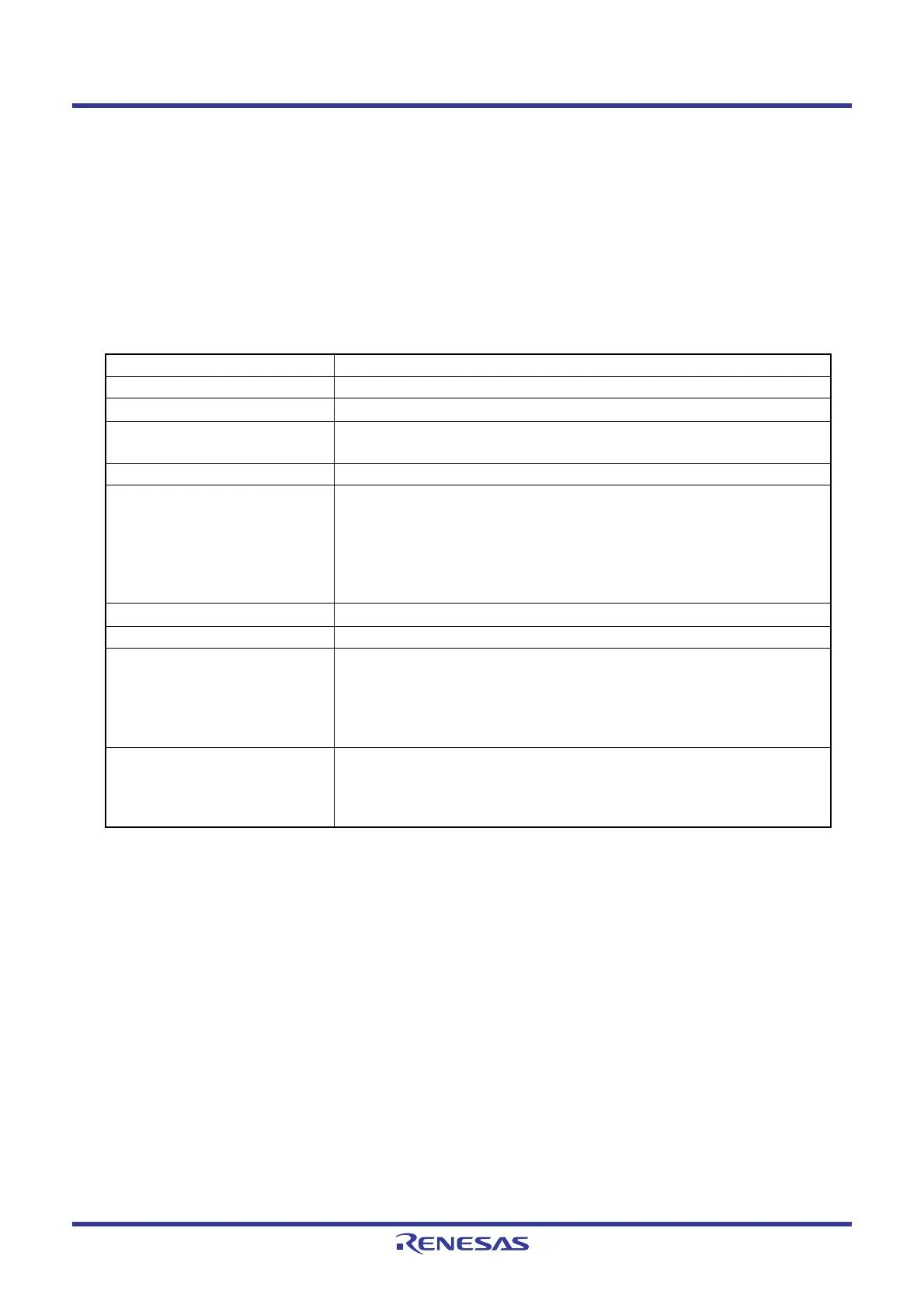

Table 17.1 Performance of A/D Converter

Item Performance

A/D conversion method Successive approximation (with capacitive coupling amplifier)

Analog input voltage

(1)

0 V to AVCC

Operating clock φAD

(2)

4.2 V ≤ AVCC ≤ 5.5 V f1, f2, f4

2.7 V ≤ AVCC < 4.2 V f2, f4

Resolution 8 bits or 10 bits selectable

Absolute accuracy AVCC = Vref = 5 V

• 8-bit resolution ± 2 LSB

• 10-bit resolution ± 3 LSB

AVCC = Vref = 3.3 V

• 8-bit resolution ± 2 LSB

• 10-bit resolution ± 5 LSB

Operating mode

One-shot and repeat

(3)

Analog input pin 4 pins (AN8 to AN11)

A/D conversion start conditions • Software trigger

Set the ADST bit in the ADCON0 register to 1 (A/D conversion

starts).

•Capture

Timer Z interrupt request is generated while the ADST bit is set to 1.

Conversion rate per pin • Without sample and hold function

8-bit resolution: 49φAD cycles, 10-bit resolution: 59φAD cycles

• With sample and hold function

8-bit resolution: 28φAD cycles, 10-bit resolution: 33φAD cycles

Loading...

Loading...