R8C/1A Group, R8C/1B Group 16. Clock Synchronous Serial Interface

Rev.1.30 Dec 08, 2006 Page 197 of 315

REJ09B0252-0130

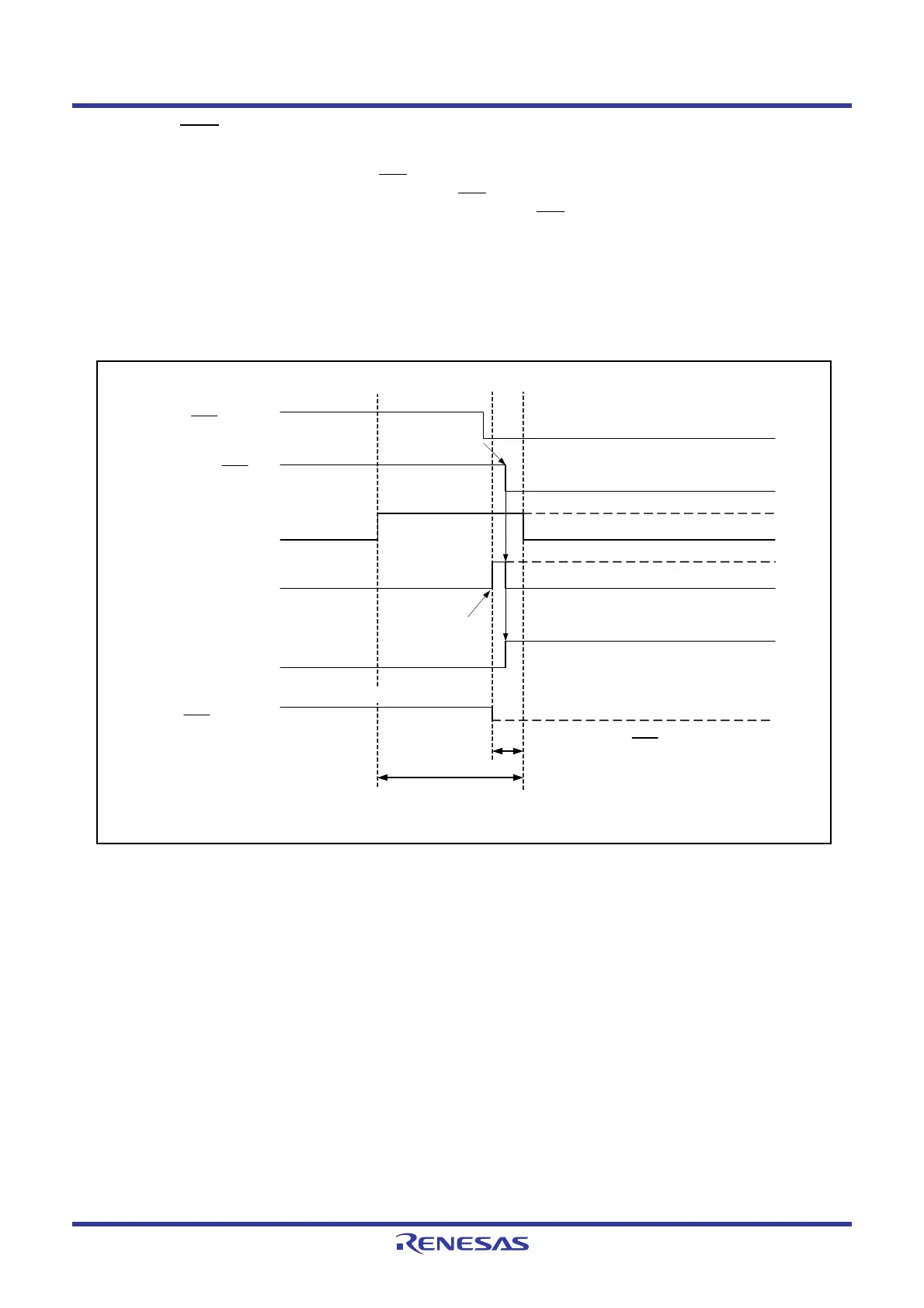

16.2.7 SCS Pin Control and Arbitration

When setting the SSUMS bit in the SSMR2 register to 1 (4-wire bus communication mode).and the CSS1 bit in

the SSMR2 register to 1 (functions as SCS

output pin), set the MSS bit in the SSCRH register to 1 (operates as

the master device) and check the arbitration of the SCS

pin before starting serial transfer. If clock synchronous

serial I/O with chip select detects that the synchronized internal SCS

signal is held “L” in this period, the CE bit

in the SSSR register is set to 1 (conflict error) and the MSS bit is automatically set to 0 (operates as a slave

device).

Figure 16.21 shows the Arbitration Check Timing.

Future transmit operations are not performed while the CE bit is set to 1. Set the CE bit to 0 (no conflict error)

before starting transmission .

Figure 16.21 Arbitration Check Timing

Data write to

SSTDR register

Maximum time of SCS internal

synchronization

During arbitration detection

High-impedance

SCS input

Internal SCS

(synchronization)

MSS bit in

SSCRH register

Transfer start

CE

SCS output

0

1

Loading...

Loading...