R8C/1A Group, R8C/1B Group 16. Clock Synchronous Serial Interface

Rev.1.30 Dec 08, 2006 Page 194 of 315

REJ09B0252-0130

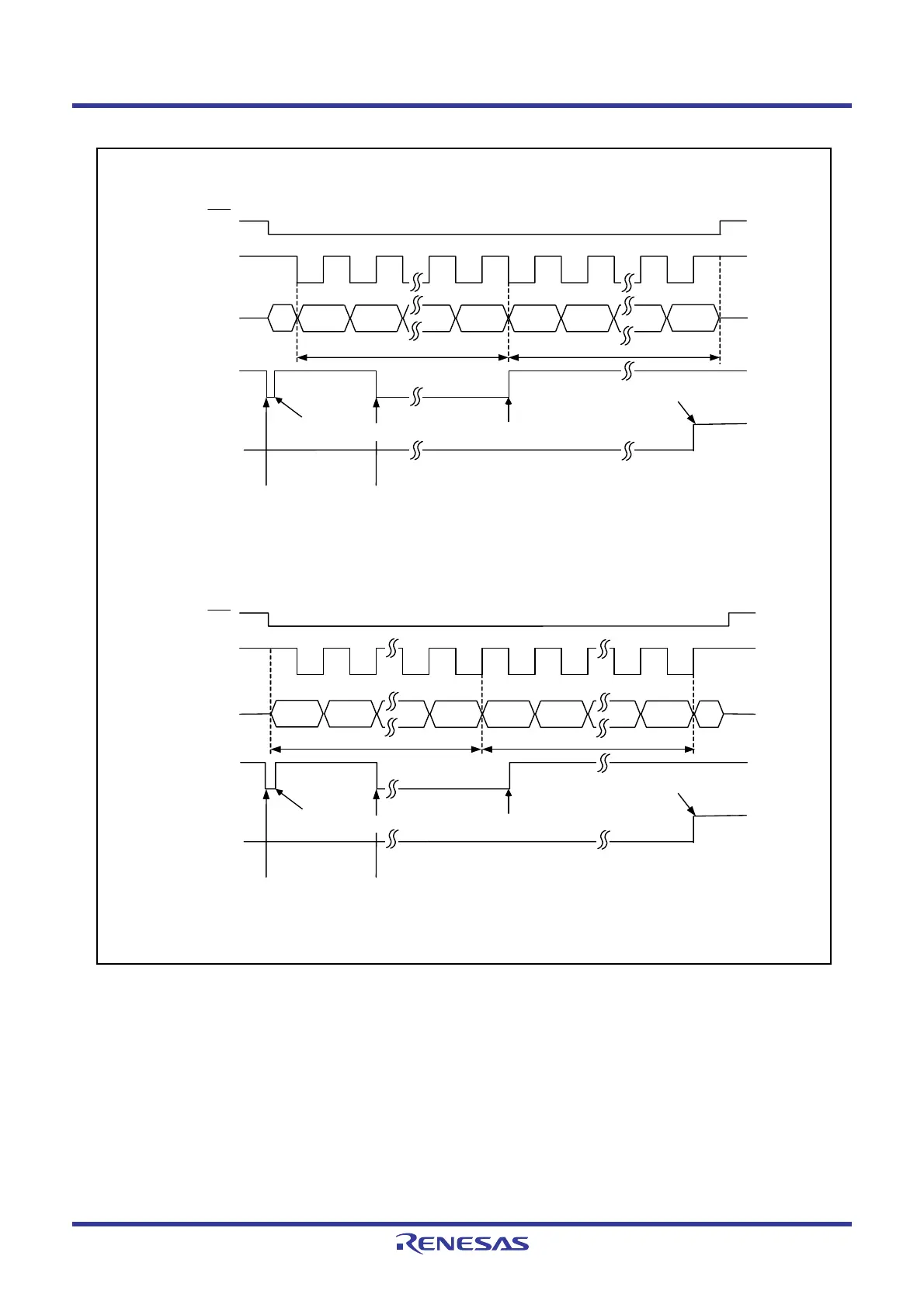

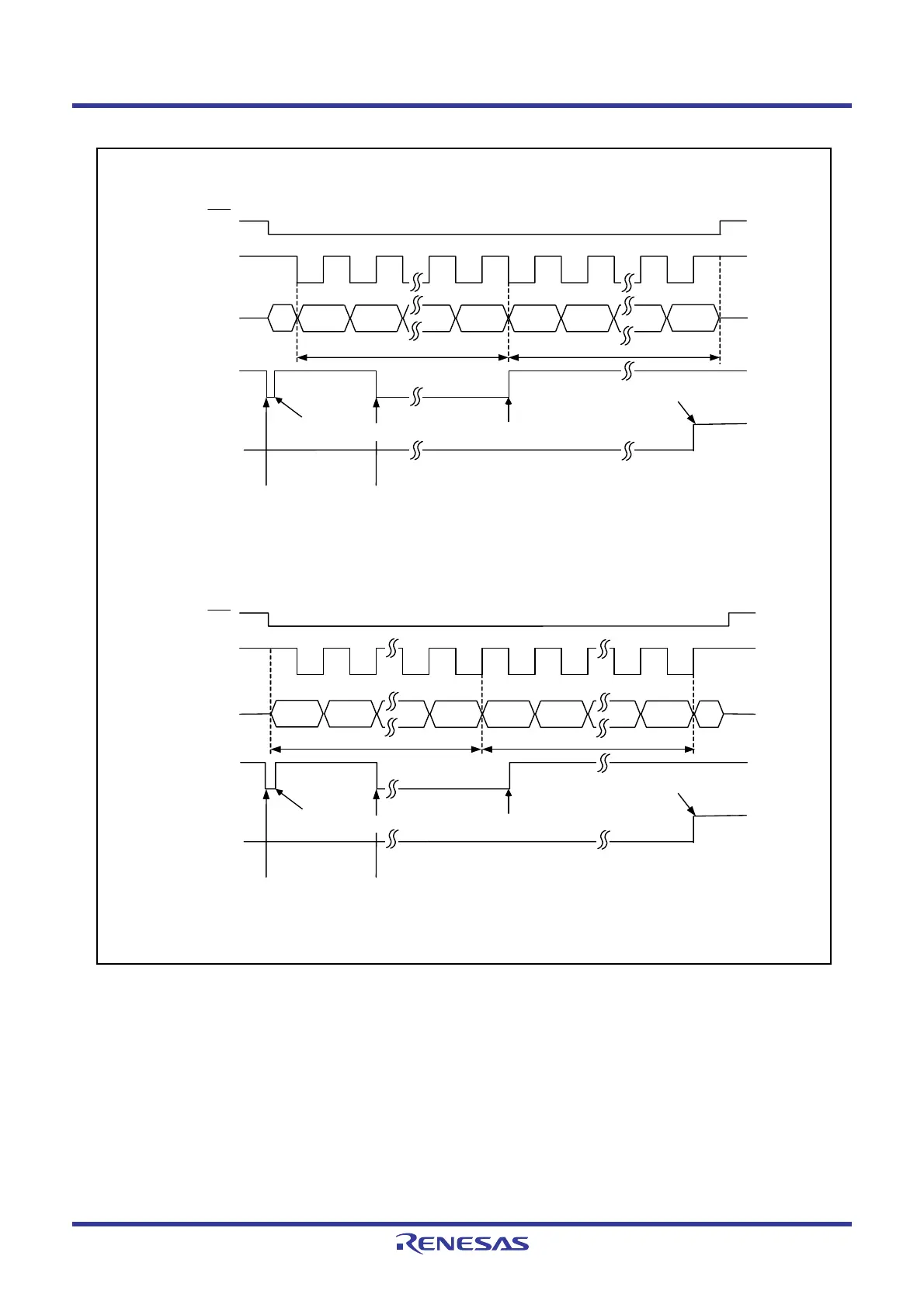

Figure 16.19 Example of Clock Synchronous Serial I/O with Chip Select Operation during Data

Transmission (4-Wire Bus Communication Mode)

TDRE bit in

SSSR register

0

1

TEND bit in

SSSR register

0

1

Data write to SSTDR register

Processing

by program

SSCK

b0SSO

• CPHS bit = 0 (data change at odd edges) and CPOS bit = 0 (“H” when clock stops)

b7

SCS

(output)

SSCK

• CPHS bit = 1 (data change at even edges) and CPOS bit = 0 (“H” when clock stops)

CPHS, CPOS: Bits in SSMR register

1 frame

TDRE bit in

SSSR register

0

1

TEND bit in

SSSR register

0

1

Data write to SSTDR register

Processing

by program

1 frame

High-impedance

b0b7

High-impedance

SCS

(output)

TXI interrupt request is

generated

b7

b0SSO

1 frame 1 frame

b6 b6

TXI interrupt request is

generated

TEI interrupt request is

generated

b6 b7

b0b6

TEI interrupt request is

generated

TXI interrupt request is

generated

TXI interrupt request is

generated

Loading...

Loading...