R8C/1A Group, R8C/1B Group 18. Flash Memory

Rev.1.30 Dec 08, 2006 Page 256 of 315

REJ09B0252-0130

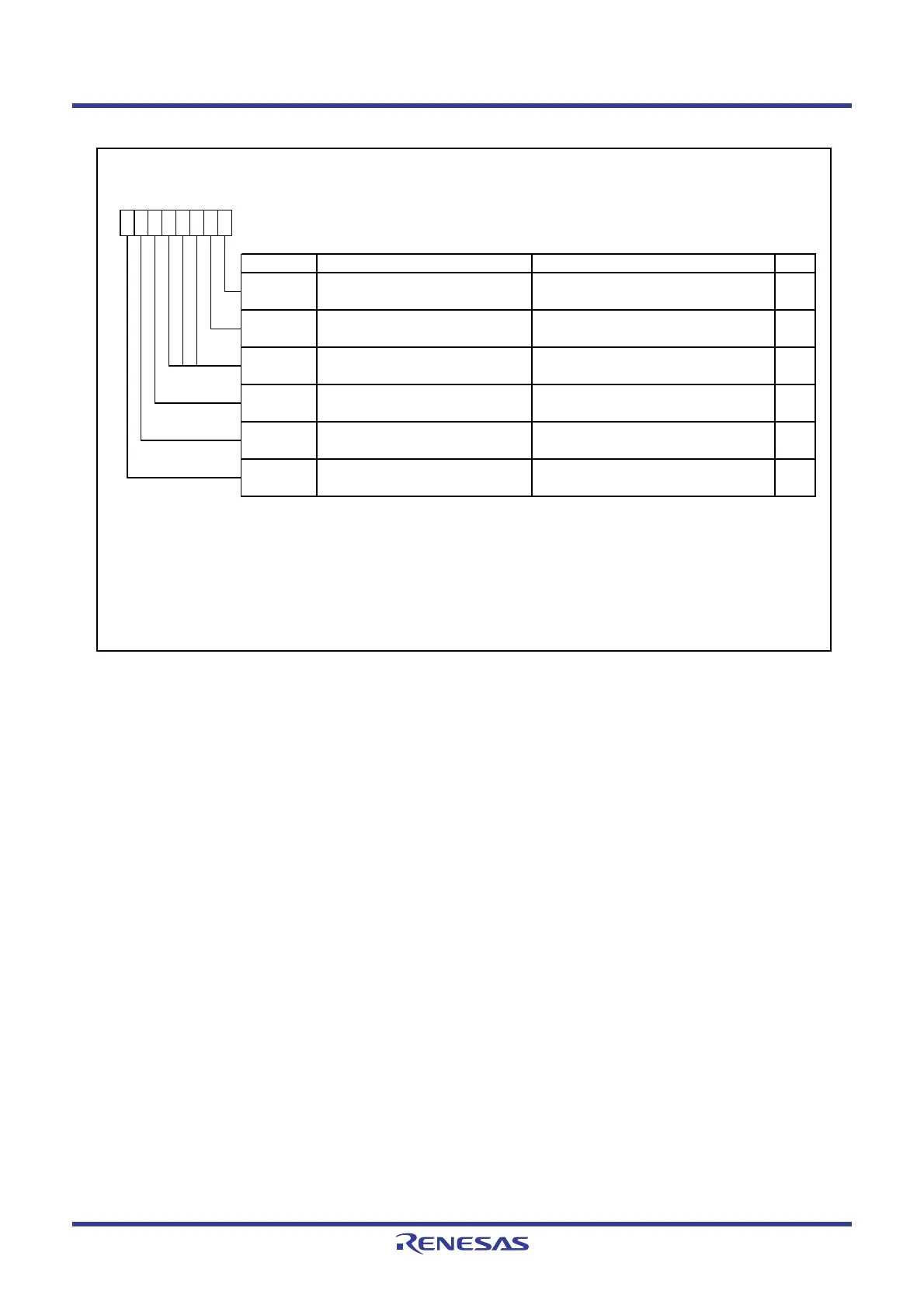

Figure 18.6 FMR1 Register

Flash Memory Control Register 1

Symbol Address After Reset

FMR1

01B5h 1000000Xb

Bit Symbol Bit Name Function RW

NOTES :

1.

2.

3.

b3 b2

Set to 0.

0

b1 b0

FMR11

—

(b4-b2)

10

b7 b6 b5 b4

RW

FMR15

—

(b0)

Reserved bits

When read, the content is undefined.

EW1 mode select bit

(1, 2)

0 : EW0 mode

1 : EW1 mode

Block 0 rew rite disable bit

(2,3)

0 : Enables rew rite.

1 : Disables rew rite.

When the FMR01 bit is set to 1 (CPU rew rite mode enabled), bits FMR15 and FMR16 can be w ritten to.

To set this bit to 0, set it to 0 immediately after setting it first to 1.

To set this bit to 1, set it to 1.

—

(b7)

0

RW

RW

RW

RO

RW

Reserved bit

0 : Enables rew rite.

1 : Disables rew rite.

FMR16

Block 1 rew rite disable bit

(2,3)

To set this bit to 1, set it to 1 immediately after setting it first to 0 w hile the FMR01 bit is set to 1 (CPU rew rite mode

enable) . Do not generate an interrupt betw een setting the bit to 0 and setting it to 1.

This bit is set to 0 by setting the FMR01 bit to 0 (CPU rew rite mode disabled).

Reserved bit Set to 1.

Loading...

Loading...