R8C/1A Group, R8C/1B Group 5. Programmable I/O Ports

Rev.1.30 Dec 08, 2006 Page 34 of 315

REJ09B0252-0130

X: 0 or 1

X: 0 or 1

X: 0 or 1

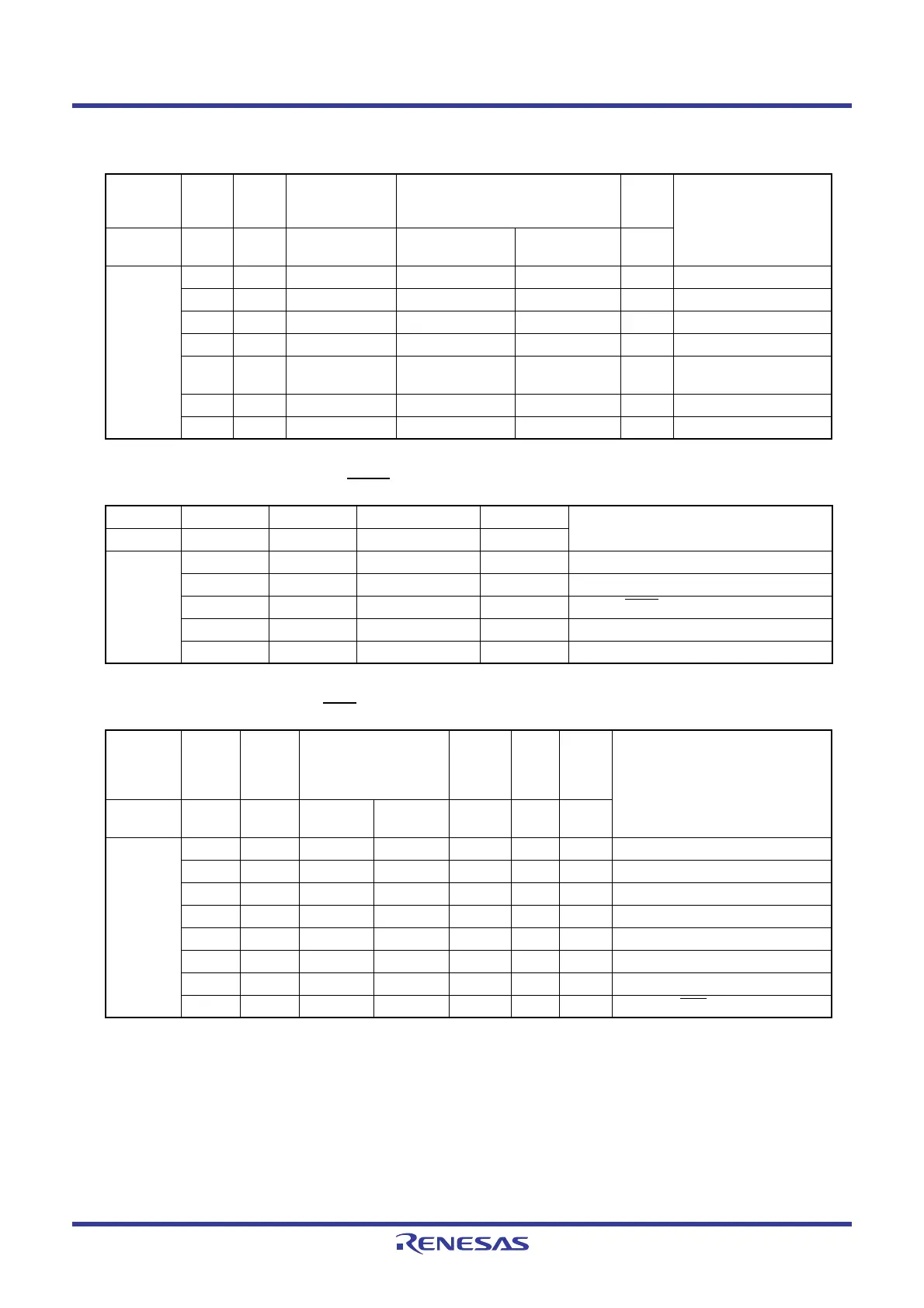

Table 5.10 Port P1_6/CLK0/SSI01

Register PD1 PUR0 U0MR

SSU (Refer to

Table 16.4 Association

between Communication Modes and

I/O Pins

)

PMR

Function

Bit PD1_6 PU03

SMD2, SMD1,

SMD0, CKDIR

SSI Output Control SSI Input Control SSISEL

Setting

Value

0 0 Other than 0X10b 0 0 X Input port (not pulled up)

0 1 Other than 0X10b 0 0 X Input port (pulled up)

0 0 XXX1b 0 0 X CLK0 (external clock) input

1 X Other than 0X10b 0 0 X Output port

X X 0X10b 0 0 X

CLK0 (internal clock)

output

X X XXXXb 0 1 1 SSI01 input

X X XXXXb 1 0 1 SSI01 output

Table 5.11 Port P1_7/CNTR00/INT10

Register PD1 PUR0 TXMR UCON

Function

Bit PD1_7 PU03 TXMOD1, TXMOD0 CNTRSEL

Setting

Value

0 0 Other than 01b X Input port (not pulled up)

0 1 Other than 01b X Input port (pulled up)

0 0 Other than 01b 0 CNTR00/INT10

input

1 X Other than 01b X Output port

X X Other than 01b 0 CNTR00 output

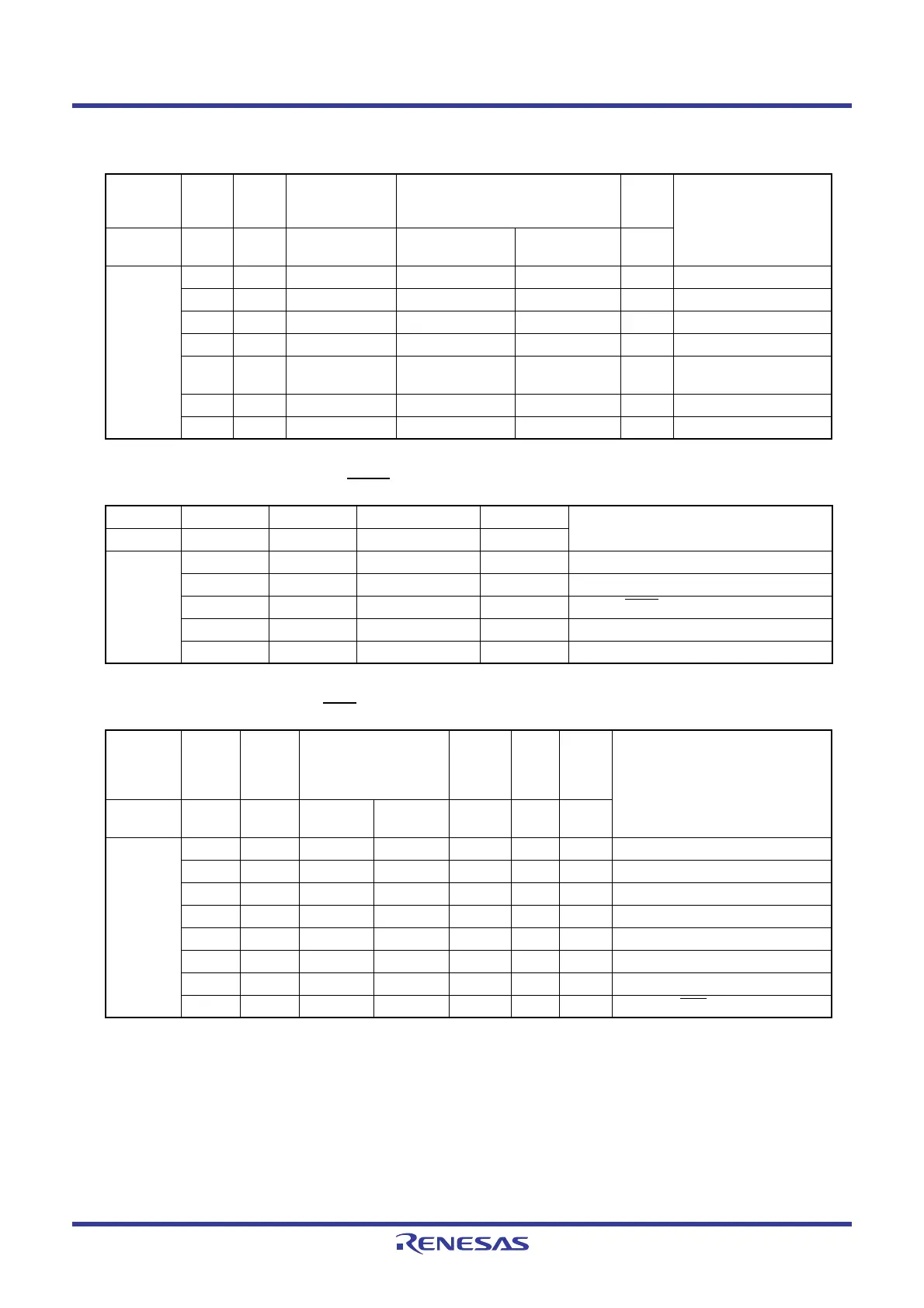

Table 5.12 Port P3_3/TCIN/INT3/SSI00/CMP1_0

Register PD3 PUR0

SSU (Refer to

Table 16.4

Association between

Communication Modes

and I/O Pins

)

TCOUT P3 PMR

Function

Bit PD3_3 PU06

SSI Output

Control

SSI Input

Control

TCOUT3 P3_3 SSISEL

Setting

Value

0 0 0 0 0 X X Input port (not pulled up)

0 1 0 0 0 X X Input port (pulled up)

X 0 0 1 X X 0 SSI00 input

1 X 0 0 0 X X Output port

X X 0 0 1 0 X Output port

X X 0 0 1 1 X CMP1_0 output

X X 1 0 X X 0 SSI00 output

0 X 0 0 0 X X TCIN input/INT3

Loading...

Loading...