R8C/1A Group, R8C/1B Group 7. Voltage Detection Circuit

Rev.1.30 Dec 08, 2006 Page 49 of 315

REJ09B0252-0130

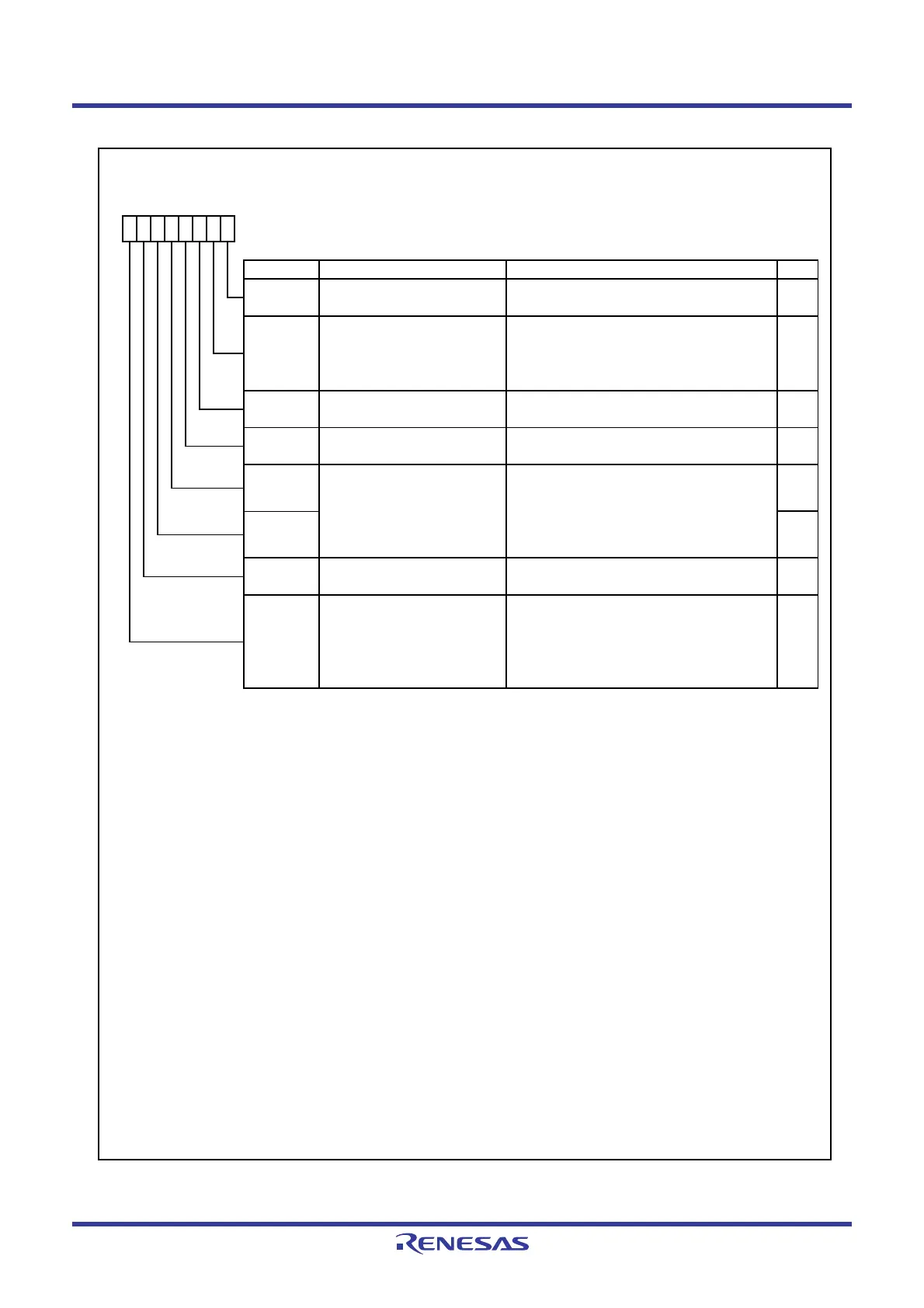

Figure 7.6 VW2C Register

Volta

e Monitor 2 Circuit Control Re

iste

(1)

Symbol Address After Reset

(8)

VW2C 0037h 00h

Bit Symbol Bit Name Function RW

NOTES :

1.

2.

3.

4.

5.

6.

7.

8.

9.

10. Set the VW2C0 bit to 0 (disabled) w hen the VCA13 bit in the VCA1 register is set to 1 (VCC

≥

Vdet2 or voltage

detection 2 circuit disabled), the VW2C1 bit is set to 1 (digital filter disabled mode), and the VW2C7 bit is set to 0

(w hen VCC reaches Vdet2 or above).

Set the VW2C0 bit to 0 (disabled) w hen the VCA13 bit is set to 0 (VCC < Vdet2), the VW2C1 bit is set to 1 (digital

filter disabled mode), and the VW2C7 bit is set to 1 (w hen VCC reaches Vdet2 or below ).

b2

0 : Not detected

1 : Vdet2 crossing detected

RW

b1 b0b3b7 b6 b5 b4

VW2C1

Voltage monitor 2 digital filter

disabled mode select bit

(2)

0 : Disable

1 : Enable

VW2C0 RW

Voltage monitor 2 interrupt /

reset enable bit

(6, 10)

VW2C3

WDT detection flag

(4,8)

0 : Not detected

1 : Detected

RW

0 : Digital filter enabled mode

(digital filter circuit enabled)

1 : Digital filter disabled mode

(digital filter circuit disabled)

RW

VW2C2

Voltage change detection

flag

(3,4,8)

VW2F1 RW

Sampling clock select bits

b5 b4

0 0 : fRING-S divided by 1

0 1 : fRING-S divided by 2

1 0 : fRING-S divided by 4

1 1 : fRING-S divided by 8

VW2F0 RW

VW2C6

Voltage monitor 2 circuit mode

select bit

(5)

0 : Voltage monitor 2 interrupt mode

1 : Voltage monitor 2 reset mode

RW

VW2C7

Voltage monitor 2 interrupt /

reset generation condition

select bit

(7,9)

0 : When VCC reaches Vdet2 or above.

1 : When VCC reaches Vdet2 or below.

RW

When the VW2C6 bit is set to 1 (voltage monitor 2 reset mode), set the VW2C7 bit to 1 (w hen VCC

reaches Vdet2 or below ). (Do not set to 0.)

Set the PRC3 bit in the PRCR register to 1 (rew rite enable) before w riting to this register.

When rew riting the VW2C register, the VW2C2 bit may be set to 1. Set the VW2C2 bit to 0 after rew riting the VW2C

register.

When the voltage monitor 2 interrupt is used to exit stop mode and to return again, write 0 to the VW2C1

bit before w riting 1.

This bit is enabled when the VCA27 bit in the VCA2 register is set to 1 (voltage detection 2 circuit

enabled).

Set this bit to 0 by a program. When 0 is w ritten by a program, it is set to 0 (and remains unchanged even if 1 is

w ritten to it).

This bit is enabled when the VW2C0 bit is set to 1 (voltage monitor 2 interrupt/reset enabled).

The VW2C0 bit is enabled w hen the VCA27 bit in the VCA2 register is set to 1 (voltage detection 2 circuit

enabled). Set the VW2C0 bit to 0 (disable) w hen the VCA27 bit is set to 0 (voltage detection 2 circuit disabled).

The VW2C7 bit is enabled w hen the VW2C1 bit is set to 1 (digital filter disabled mode).

Bits VW2C2 and VW2C3 remain unchanged after a softw are reset, w atchdog timer reset, or voltage monitor 2 reset.

Loading...

Loading...