SIM/LIM – set/read interrupt

condition code mask (UAMW)

The interrupt mask "masks" interrupts in the interrupt condition code

word until the end of the cycle, i.e. all interrupts remain pending, but

the program is not interrupted by them.

Bit in the interrupt condition code mask = 0: interrupt disabled

Bit in the interrupt condition code mask = 1: interrupt enabled

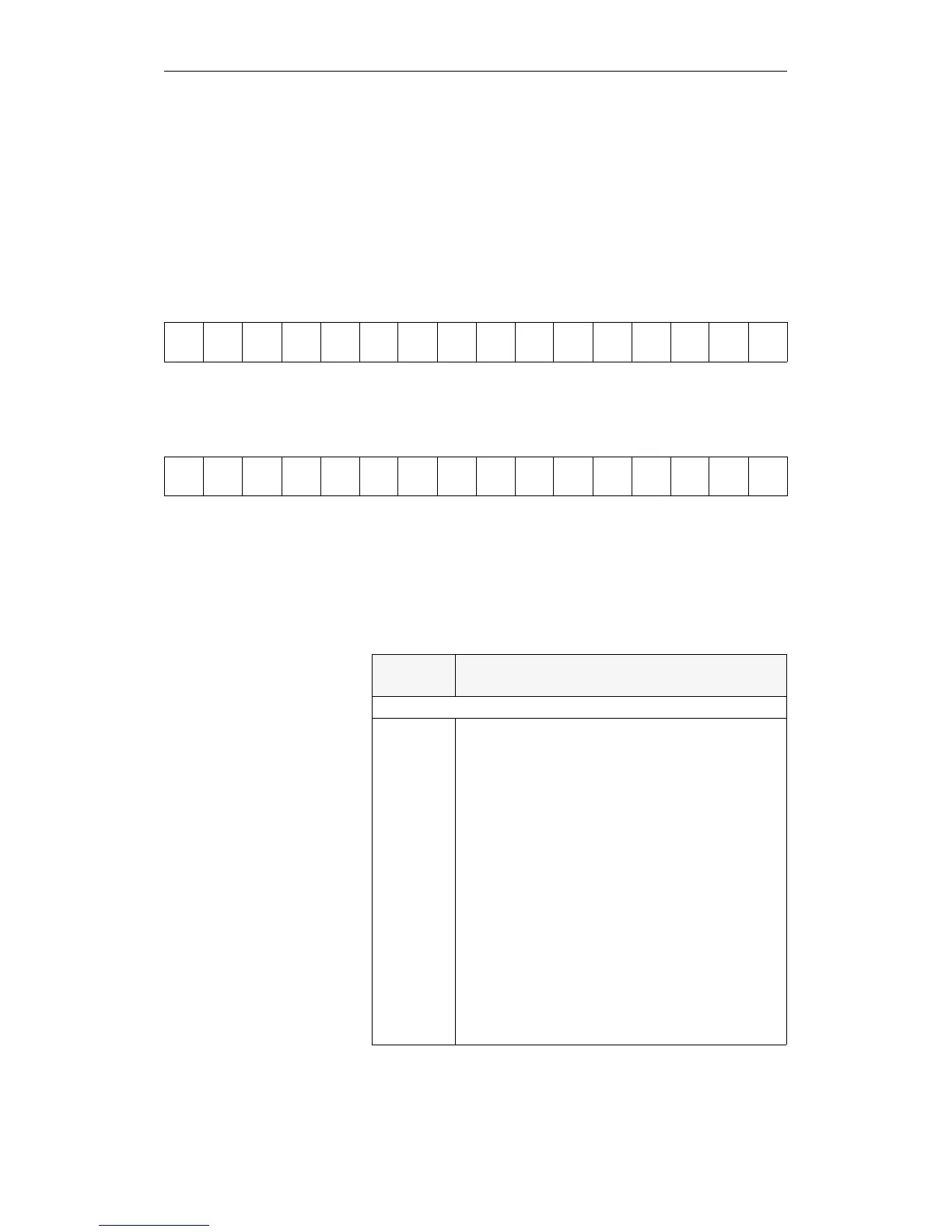

Meaning of the bits in UAMW-H or ACCU-1-H:

15 8 7 0

INTX INTE INTF INTG WEFE WA PA BULE PEU HALT ES AV INTAS TAU DARY KZU

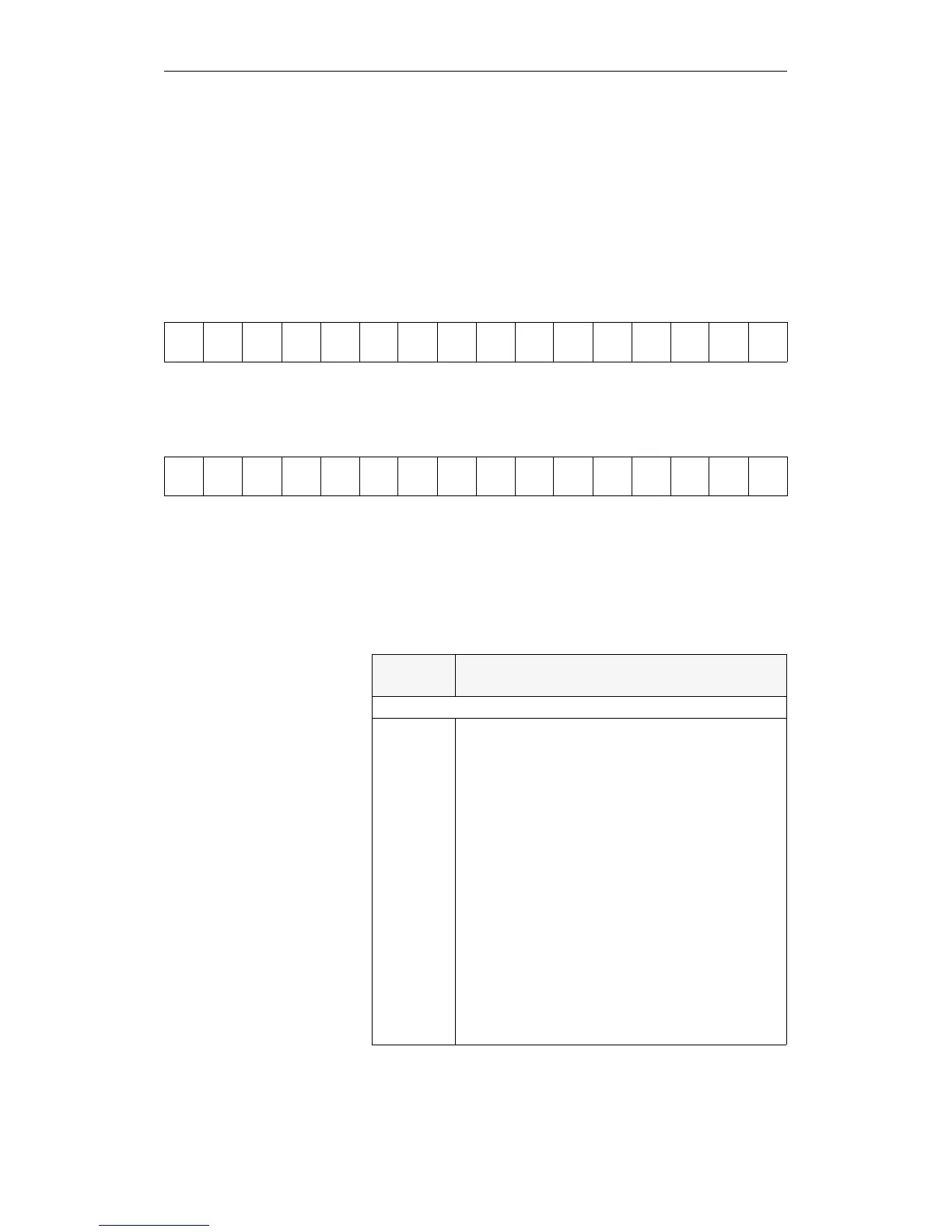

Meaning of the bits in UAMW-L or ACCU-1-L:

15 8 7 0

– KB KDB STS TLAF SUF STUEBSTUEU NAU ZA QVZ ADF PARE ZYK STOP HOLD

Abbrev. Meaning

High word

INTX

INTE

INTF

INTG

WEFE

WA

PA

BULE

PEU

HALT

ES

AV

INTAS

TAU

DARY

KZU

S5 bus/system interrupt A, B, C or D (slot-

dependent)

S5 bus/system interrupt E

S5 bus/system interrupt F

S5 bus/system interrupt G

Collision of timed interrupts

Timed interrupt

Process interrupt

Bus lock error

I/Os not ready

Stop instruction from coordinator COR

Single step mode

Address comparison active

Interrupt from SPU processor

Clock failure of SPU processor

Continuous ready (access to faulty memory)

Bracket counter overflow

Table 3-28 Meaning of the abbreviations in UAMW

Executive Operations

CPU 948 Programming Guide

C79000-G8576-C848-04

3 - 73

Loading...

Loading...