Error address

If a parity error or timeout occurs, the address that caused the error can

be read out of the system data area (refer to Chapter 8):

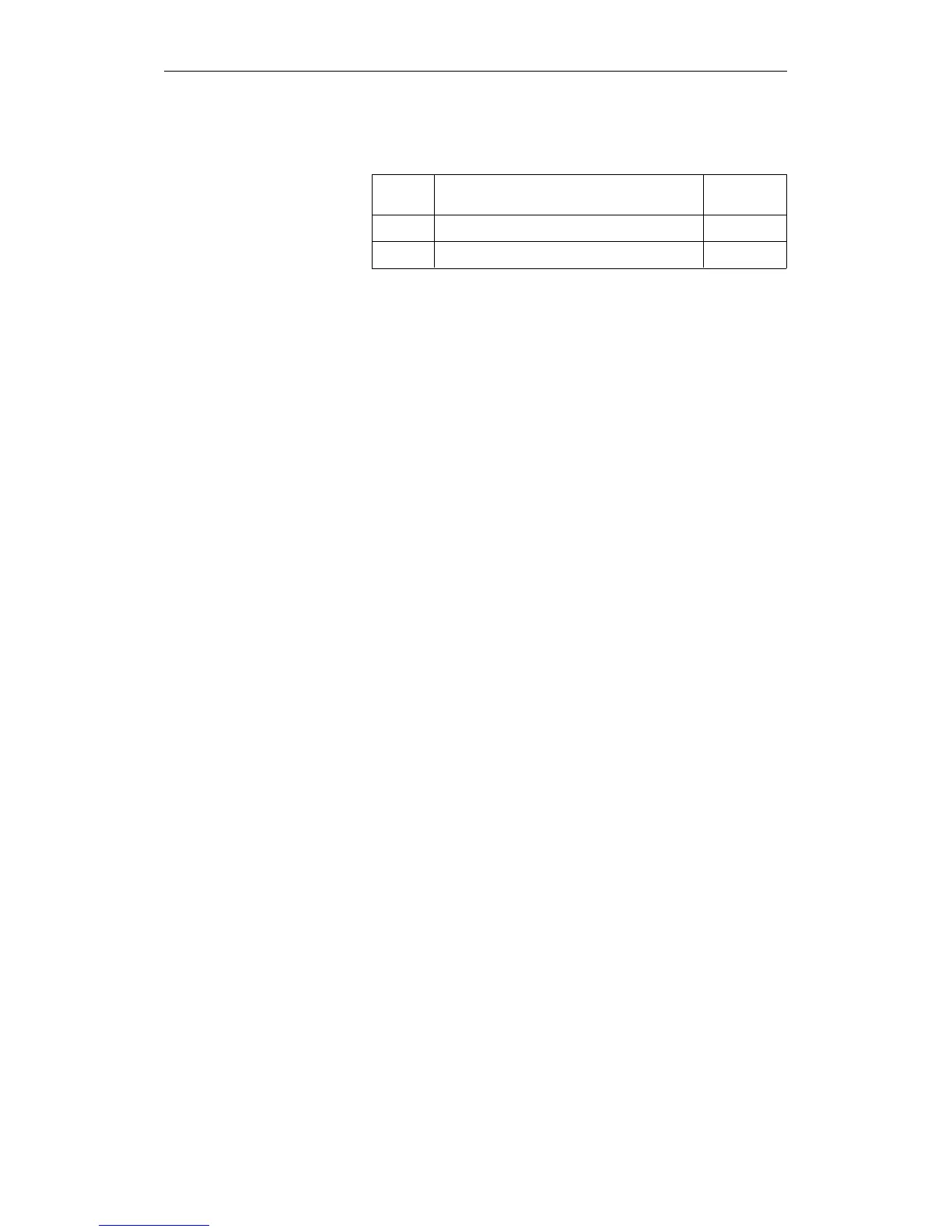

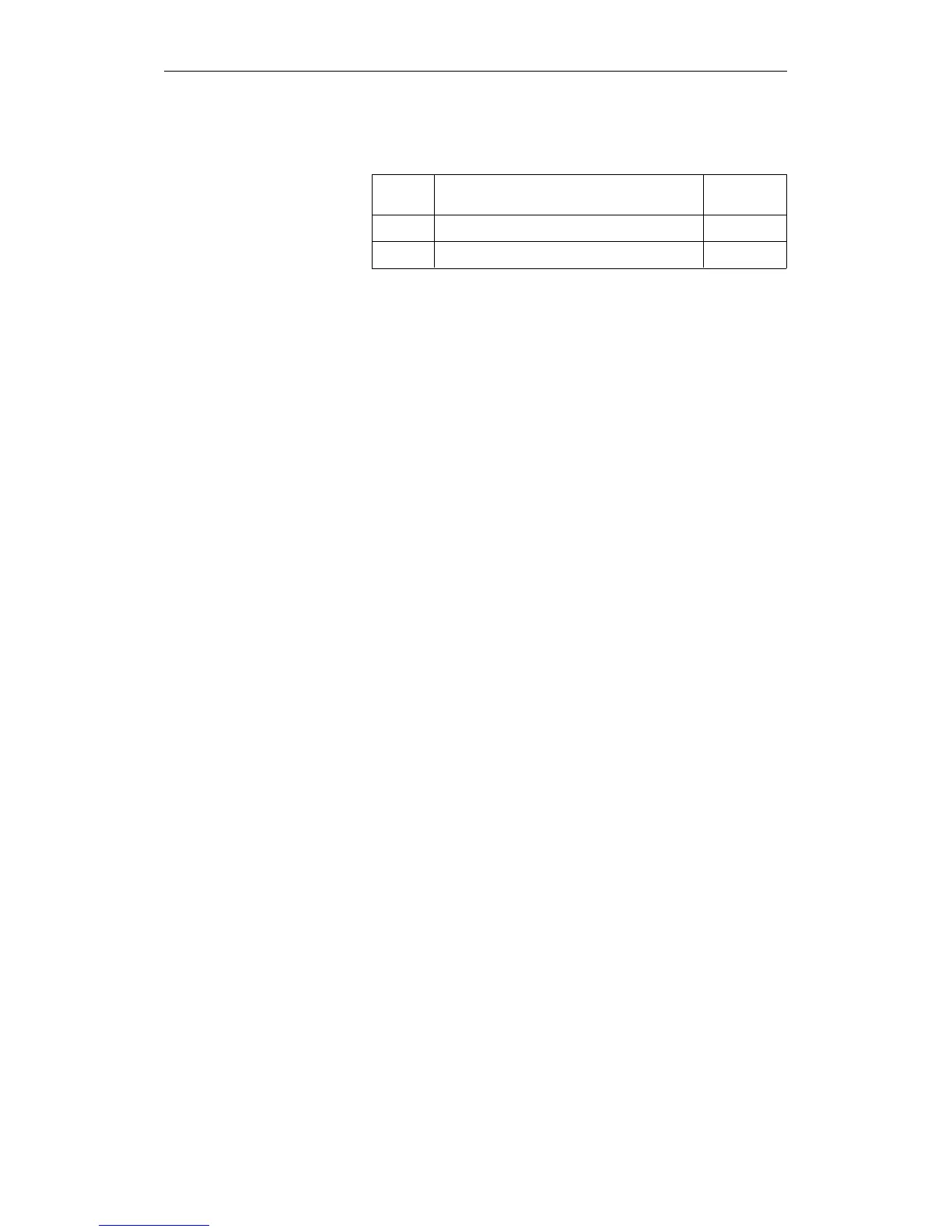

RS Contents Address

70 PARE error address high E F046H

71 PARE error address low E F047H

5.6.8

OB 32: Load and Transfer

Error (TRAF)

A load and transfer error is indicated in the following situations:

•• When accessing data in data blocks or extended data blocks, the

CPU compares the length of the opened block to the parameter in

the load or transfer operation.

If the specified parameter exceeds the actual data block length, the

CPU does not execute the load or transfer operation. This prevents

data in the memory from being overwritten by mistake during

transfer operations. With load errors, the contents of the

accumulator are retained.

•• A load or transfer error is also detected if a single bit within a

non-existent data word is to be scanned or changed.

•• If no data block has yet been opened (with "C DBn" or

"CX DXn") prior to access to a data word, this also causes a

load/transfer error.

•• Accessing the memory using incorrect absolute addresses via the

BR register or incorrect area boundaries with the "TNW", "TXW"

and "TXB" operations can cause a load or transfer error.

When the system program detects a load or transfer error, it calls

OB 32, if this is loaded. The operation that caused the load or transfer

error is not processed.

If OB 32 is not loaded, the CPU changes to the STOP mode.

Causes of Error and Reactions of the CPU

CPU 948 Programming Guide

C79000-G8576-C848-04

5 - 29

Loading...

Loading...